## Leakage Assessment on Elephant\_first\_order

9/23/2022 Jens-Peter Kaps

Kris Gaj

1. Target

a) Algorithm: Elephant

b) Implementer: Ruhr-University Bochum, Germany

c) Variant: **Elephant\_first\_order**

Abubakr Abdulgadir

d) URL: https://github.com/Chair-for-Security-Engineering/LWC-Masking

e) Commit hash: 4e954f283f0bf7ec25ca49f811e51df32fb2e9f0

f) Protection method: Hardware Private Circuits 2 (HPC2)

g) Protection order: 1

2. Equipment and Software Used

(a) General type of the evaluation platform: **Control board is FOBOS3 board for control. This board uses a PYNQ-Z1 board with a Zynq SoC (XC7Z020-1CLG400C) and a custom board that hosts an ADC for power measurement. The target board is NewAE CW305 Aritx7** (xc7a100tftg256)

(b) Oscilloscope and its major characteristics: **We utilized OpenADC with 40 MHz bandwidth and a maximum sampling rate of 100 MS.**

(c) Current and electromagnetic probes: N/A

(d) Usage of bandwidth limiters, filters, amplifiers, etc. and their specification: **Power was measured at the output of the CW305's onboard amplifier which amplifies the voltage drop across the board's 0.1**  $\Omega$  **shunt resistor.**

(e) Are sampling clock and design-under-evaluation clock synchronized? Yes

(f) Names and versions of programs used for evaluating side-channel resistance: **FOBOS3 analysis software.**

g) Clock frequency of target: **10 MHz**

h) Sampling frequency and resolution: **50 M Sample/sec sampling frequency and 10 bit resolution.**

3. Leakage Assessment Method

a) Type of the method: Fixed-vs-random Test Vector Leakage Assessment [GJJR11,SM15].

b) Number of traces: **100,000 traces.**

c) Source of randomness: Trivium-based DRBG.

Before each test vector is processed, the DRBG is run to store the required number of random words in a FIFO. The design-under-evaluation then consume randomness from the FIFO and the DRBG is disabled while the design-under-evaluation is running. The goal of this is to eliminate the effect of the DRBG power consumption on the measurements.

d) Trigger location relative to the execution start time of the algorithm: **Triggered ADC at the start of the algorithm.**

e) Time required to collect data for a given attack/leakage assessment: 35 minutes.

f) Total time of the attack/assessment: 35 minutes.

g) Total size of all traces (if stored): **2.4 GB.**

h) Availability of raw measurement results: Per request.

i) Test vector generation:

The test vectors used and the scripts used for generation are available in the attached file.

The procedure is as follows:

1- Generate a short unshared test vector using cryptotvgen.

2- Convert it into a shared format using gen\_shared.py.

3- Generate the FOBOS-ready fixed-vs-random test vectors using lwc\_2\_fobos\_tv.py. The SDI is kept similar in all test vectors, and the PDI section is fixed in fixed test vectors and random in the random test vectors. Fresh sharing on the PDI section is generated in all test vectors.

4. Results:

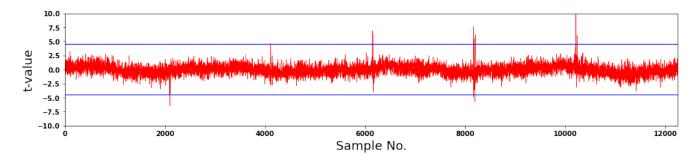

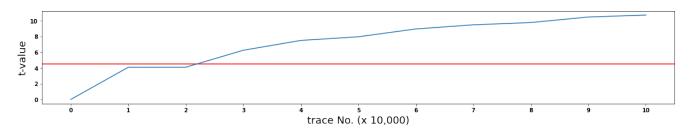

a) Documentation of results: **Figure 1 shows first-order TVLA using 100,000 traces. Figure 2 shows t-values vs. number of traces processed. Listing 1 shows the clock cycles where t-values exceed the threshold for the test vectors attached.**

Figure 1: TVLA results for Elephant\_first\_order (100,000 traces)

Figure 2: Elephant\_first\_order maximum t-value vs. number of traces (x 10,000)

**Listing 1**: Samples that exceed the 4.5 threshold (For the attached test vectors) sample--clk--tvalue 2095 --419 -- -6.5 4110 --822 -- 4.6 6145 --1229 -- 6.9 6146 --1229 -- 5.8 6150 --1230 -- 6.8 6155 --1231 -- 6.4 6156 --1231 -- 4.9 8165 --1633 -- -4.9 8166 --1633 -- -4.8 8170 --1634 -- 7.7 8171 --1634 -- 5.6 8175 -- 1635 -- 5.6 8195 --1639 -- -5.7 8196 --1639 -- -5.2 8205 --1641 -- 6.2 8206 --1641 -- 4.9 10210 --2042 -- 4.5 10215 --2043 -- 10.7 10216 --2043 -- 6.1 10235 --2047 -- 6.1

## References

[GJJR11] G. Goodwill, B. Jun, J. Jaffe, and P. Rohatgi, "A testing methodology for side-channel resistance validation," Nara, Japan, 2011.

[SM15] T. Schneider and A. Moradi, "Leakage Assessment Methodology - a clear roadmap for sidechannel evaluations," Cryptology ePrint Archive 2015/207, Jun. 2015. Accessed: Dec. 31, 2021. [Online]. Available: <u>https://eprint.iacr.org/2015/207</u>