# **ECE-493**

# FINAL REPORT

# NES Handheld Emulation Breakout Board for the BASYS-3

# Abstract

There are several methods to emulate the NES, including software or hardware emulation, with the latter being a more authentic emulation. We emulated the NES on a BASYS-3 Artix-7 FPGA and minimized overall cost of components needed to create a portable/handheld device. Our NES FPGA emulation device will be comparable to existing devices in terms of price and capabilities. We used existing functionalities of power systems and of P-MOD accessories for the BASYS-3 to create a singular breakout PCB to interface with the BASYS-3. Additionally, this project is designed to be open source to allow future expansion of capabilities and to provide an opportunity to learn about retro console emulation.

Team Members: Joshua Thomas Riggs, Brooks Aaron Corbett, Anthony Thinh Tang, Samuel Kifle Kebadu, Amilcar Alejandro Paniagua Date of Submission: 12/4/2022 Faculty Supervisor: Dr. Jens-Peter Kaps

# **Executive Summary**

Current options for Nintendo Entertainment System (NES) emulation, with the requirements of being portable and hardware emulated, are limited and costly. In response, our solution is to design a breakout printed circuit board (PCB) with necessary interfaces and inputs/outputs for the BASYS-3 Artix-7 Field Programmable Gate Array (FPGA), to design an 3D-printed encasing for the purpose of being portable/handheld, and to include cost effective components such as the LCD screen, battery, SD card, and audio speaker. This project results in allowing the BASYS-3 to be a new platform for NES emulation and in providing a new option for DIY NES emulation. Our team is composed of five members, majoring in Computer Engineering and Electrical Engineering:

| Team Member              | Relevant Experience    | Skills                      |  |

|--------------------------|------------------------|-----------------------------|--|

| Samuel Kebadu (CpE) (PM) | ECE 445, 446, 447, 448 | Verilog, VHDL, C++, C,      |  |

|                          | FPGA Internship        | Computer Architecture       |  |

| Amilcar Paniagua (CpE)   | ECE 286, 447, 448      | VHDL, C++, C, Circuit       |  |

|                          |                        | Design, Soldering, PCB      |  |

|                          |                        | Design                      |  |

| Brooks Corbett (EE)      | ECE 286, 447, 436      | Circuit Design, PCB Design, |  |

|                          | Hardware Engineering   | Power system design,        |  |

|                          | Internship             | Soldering,                  |  |

| Joshua Riggs (EE)        | ECE 448, 445, 436, 447 | VHDL, Digital Design, PCB   |  |

|                          |                        | Design                      |  |

| Anthony Tang (EE)        | ECE 286, 445, 447, 436 | AutoCAD, Circuit Design,    |  |

|                          |                        | Soldering, C                |  |

CpE: Computer Engineering PM: Project Manager EE: Electrical Engineering

# **Table of Contents**

| 1. | Apj  | proa | ch                              | 6  |

|----|------|------|---------------------------------|----|

|    | 1.1  | Orig | gin                             | 6  |

|    | 1.2  | Solu | ution                           | 6  |

|    | 1.3  | Alte | ernative Designs                | 7  |

|    | 1.4  | Tea  | m Member Contributions          | 8  |

| 2. | Tec  | hnic | al section                      | 9  |

|    | 2.1  | Fun  | ction Decomposition (Level 0)   | 9  |

|    | 2.2  | Fun  | ction Decomposition (Level 1) 1 | 0  |

|    | 2.3  | Fun  | ction Decomposition (Level 2) 1 | .1 |

|    | 2.4  | Sys  | tem Architecture 1              | 4  |

|    | 2.5  | Da   | taflow 1                        | 5  |

|    | 2.6  | Stat | e Diagram 1                     | 6  |

|    | 2.7  | Circ | cuit Schematics 1               | 7  |

|    | 2.7. | 1    | Controller 1                    | 7  |

|    | 2.7. | 2    | Power/Charging 1                | 8  |

|    | 2.7. | 3    | Audio1                          | 9  |

|    | 2.7. | 4    | Memory                          | 20 |

|    | 2.7. | 5    | Display                         | 21 |

|    | 2.8  | Sof  | tware                           | 2  |

|    | 2.8. | 1    | Rebuild2                        | 22 |

|    | 2.8. | 2    | Start Menu                      | 22 |

|    | 2.8. | 3    | Game Storage                    | 23 |

|    | 2.9  | Har  | dware                           | 24 |

|    | 2.9. | 1    | VGA to HDMI                     | 24 |

|    | 2.9. | 2    | SD Card                         | 24 |

|    | 2.9. | 3    | BASYS-3                         | 25 |

|    | 2.9. | 4    | Display                         | 25 |

|    | 2.9. | 5    | Battery2                        | 26 |

|    | 2.9. | 6    | PCB                             | 26 |

|    | 2.9. | 7    | CAD                             | 28 |

|         | 2.9.                                                   | .7.1 3D Models                                                                                                                                                                       | 28                                                                                             |

|---------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|         | 2.9.                                                   | .7.2 Orthographic Projections (mm)                                                                                                                                                   | 33                                                                                             |

|         | 2.9.                                                   | .7.3 3D Print Results                                                                                                                                                                | 37                                                                                             |

| 3.      | Exp                                                    | perimentation                                                                                                                                                                        | 41                                                                                             |

| -       | 3.1                                                    | Introduction                                                                                                                                                                         | 41                                                                                             |

|         | 3.2                                                    | Audio and Video Synchronization                                                                                                                                                      | 42                                                                                             |

|         | 3.2.                                                   | .1 Experiment Introduction                                                                                                                                                           | 42                                                                                             |

|         | 3.2.                                                   | .2 Results                                                                                                                                                                           | 42                                                                                             |

|         | 3.3                                                    | Button Response Time                                                                                                                                                                 | 43                                                                                             |

|         | 3.3.                                                   | .1 Experiment Introduction                                                                                                                                                           | 43                                                                                             |

|         | 3.3.                                                   | .2 Results                                                                                                                                                                           | 43                                                                                             |

|         | 3.4                                                    | Battery Lifetime on Full Charge                                                                                                                                                      | 44                                                                                             |

|         | 3.4.                                                   | .1 Experiment Introduction                                                                                                                                                           | 44                                                                                             |

|         | 3.4.                                                   | .2 Results                                                                                                                                                                           | 44                                                                                             |

| 4.      | Exp                                                    | periment Validation                                                                                                                                                                  | 45                                                                                             |

| 5.      | Pro                                                    | oject Lifetime                                                                                                                                                                       | 46                                                                                             |

| -       | 5.1                                                    | Maintainability/Maintenance of Final Design                                                                                                                                          | 46                                                                                             |

| -       | 5.2                                                    | End of Project's Lifetime                                                                                                                                                            | 46                                                                                             |

| 6.      | Ad                                                     | ministration                                                                                                                                                                         | 47                                                                                             |

| (       | 6.1                                                    | Progress                                                                                                                                                                             | 47                                                                                             |

| (       | 6.2                                                    | Changes to Design                                                                                                                                                                    | 48                                                                                             |

| (       | 6.3                                                    |                                                                                                                                                                                      |                                                                                                |

|         | 0.5                                                    | Unplanned Activities                                                                                                                                                                 | 50                                                                                             |

| (       | 6.4                                                    | -                                                                                                                                                                                    | 50<br>51                                                                                       |

|         |                                                        |                                                                                                                                                                                      | 51                                                                                             |

| (       | 6.4<br>6.5                                             | Funds Spent                                                                                                                                                                          | 51<br>52                                                                                       |

| 7.      | 6.4<br>6.5                                             | Funds Spent<br>Man-hours Spent                                                                                                                                                       | 51<br>52<br>53                                                                                 |

| 7.<br>, | 6.4<br>6.5<br><b>Les</b>                               | Funds Spent<br>Man-hours Spent                                                                                                                                                       | 51<br>52<br>53<br>53                                                                           |

| 7.<br>, | 6.4<br>6.5<br><b>Les</b><br>7.1                        | Funds Spent<br>Man-hours Spent<br>ssons learned<br>Skills<br>Knowledge                                                                                                               | 51<br>52<br>53<br>53<br>53                                                                     |

| 7.<br>, | 6.4<br>6.5<br><b>Les</b><br>7.1<br>7.2                 | Funds Spent         Man-hours Spent         ssons learned         Skills         I         Verilog                                                                                   | 51<br>52<br>53<br>53<br>53<br>53                                                               |

| 7.<br>, | 6.4<br>6.5<br><b>Les</b><br>7.1<br>7.2<br>7.2.         | Funds Spent         Man-hours Spent         ssons learned         Skills         Knowledge         .1         Verilog         .2         PCB Design                                  | <ol> <li>51</li> <li>52</li> <li>53</li> <li>53</li> <li>53</li> <li>53</li> <li>54</li> </ol> |

| 7.<br>, | 6.4<br>6.5<br><b>Les</b><br>7.1<br>7.2<br>7.2.<br>7.2. | Funds Spent         Man-hours Spent         ssons learned         Skills         Knowledge         .1         Verilog         .2       PCB Design         .3       6502 Architecture | 51<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>54                                             |

| 9.  | Appendix A: Proposal (ECE-492)                    | 56  |

|-----|---------------------------------------------------|-----|

| 10. | Appendix B: Design Document (ECE-492)             | 74  |

| 11. | Appendix C: Software printout – if required by FS | 114 |

| 1   | 1.1 ECE493TESTER.c                                | 114 |

# 1. Approach

### 1.1 Origin

Since original NES consoles are not commercially sold anymore, or are expensive to purchase secondhand, we wanted to develop a cheaper alternative that still maintains portability and simplicity. In addition, some current market alternatives use hardware locked FPGAs; we have planned to have our NES FPGA project to be "unlocked" to allow programmability to the BASYS-3 in case the user desires to use the FPGA platform for other purposes.

#### **1.2 Solution**

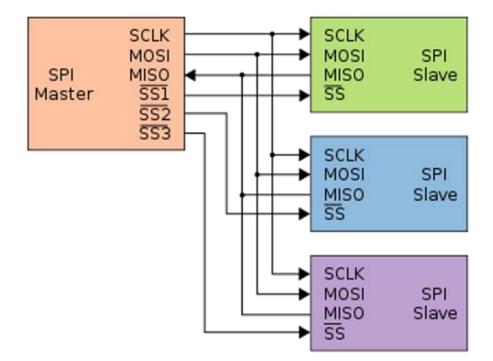

In order to prototype our project, we started with the BASYS-3 and hardware language. Credit is given to Brian Bennett, who provided his recreation of the NES architecture written in Verilog, available to the public on GitHub [3]. Input and output signals in the constraints file were adjusted to match the P-MOD pins of the BASYS-3. A VGA display, an NES controller, and an audio speaker were required to playtest the emulated NES, along with two BASYS-3 PMOD expansions for audio amplification and SD card reading. The NES architecture can be stored in the BASYS-3 as its default program via USB Universal Asynchronous Receiver-Transmitter (UART) communication, which can also load the NES game ROMs. This functionality was planned to be integrated into the Verilog code to read game ROMs from an SD card through Serial Peripheral Interface (SPI).

Additional components, such as a small LCD screen and a battery power source, were chosen to allow the device to have portable/handheld functionality. To minimize the dimensions of our device, we designed and printed our own breakout PCB that contains the audio amplifier

circuit, SD card reading circuit, button interface circuit, video output circuit, and power management circuit.

#### **1.3 Alternative Designs**

There were possible several alternatives that were considered:

- External display, controllers, and audio instead of embedded

- Not using the BASYS-3, instead simply using an FPGA soldered to the breakout board

- Using a different storage solution as opposed to an SD card i.e., memory bank

- Using a wired power connection as opposed to battery

Using external components would make the device lose its portability and handheld functionality. Next, switching out the BASYS-3 with a soldered FPGA to the breakout board would minimize the device's dimensions. Another alternative was using a memory bank in the BASYS-3 to store game ROMs; however, this would disallow a user to "plug and play" their own game ROMS via SD card. The last alternative was to use a wired power connection and eliminate the use of a battery. Handheld functionality can be preserved but portability of the device would be lost. These alternatives would have greatly shifted the time and budget specifications of this project.

As mentioned before, Brian Bennett's FPGA project of the NES architecture on GitHub was implemented into the BASYS-3. He reported that his project is missing mappers and the Delta Modulation Channel (DMC). He also provided a C++ windows application named NesDbg that will allow communication to the FPGA via USB UART. NesDbg can be used to run tests and to load game ROMs.

#### **1.4 Team Member Contributions**

Our project will consist of five main tasks:

- o Circuit design

- o PCB design

- Enclosure design

- Game selection menu program

- RTL code for memory

Brooks was responsible for circuit design, with the help of Anthony. Their objective was to design the circuitry and schematics for the breakout board in EasyEDA. Simulations were conducted in computer SPICE software by Amilcar.

Amilcar was responsible for designing the PCB layout, with the help of Brooks. They used the circuits designed by Brooks and Anthony to design a PCB layout in EasyEda. They were responsible for soldering required electronic components to the PCB and testing/debugging the PCB.

When the breakout board dimensions and externals were finalized, Anthony had the responsibility of designing the 3D-printed enclosure with the help of Amilcar. They constructed the device with all the necessary large components such as the LCD screen and the battery in mind.

While the tasks above were sequential, Josh and Sam helped one another on the software/RTL responsibilities. Sam's main responsibility was to create code for RTL functionality for manipulating memory locations in the memory map on the NES architecture. Josh, in tandem, was responsible for programming and designing a game selection menu on boot-up to work with the RTL design.

# 2. Technical section

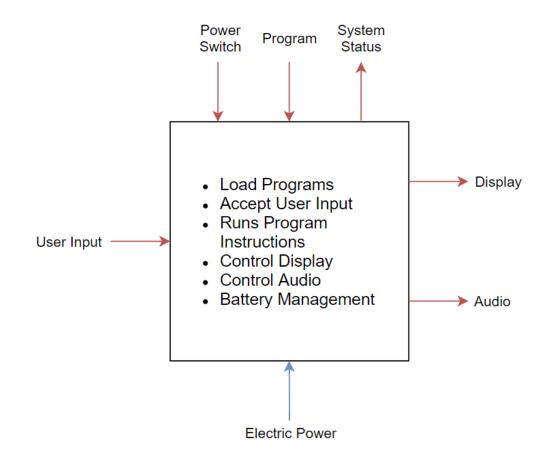

#### **2.1 Function Decomposition (Level 0)**

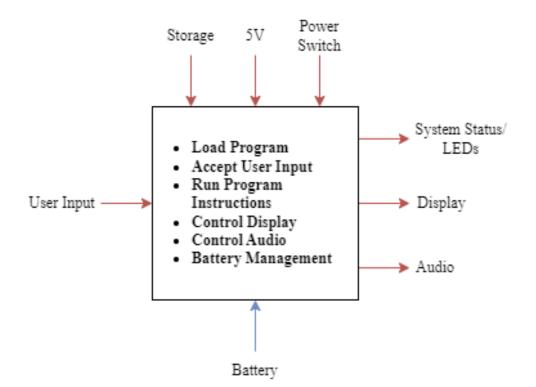

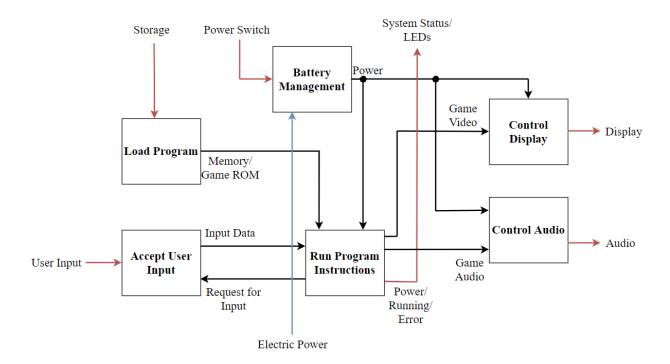

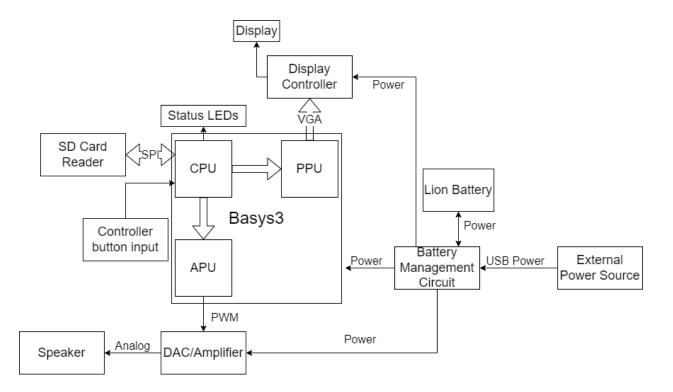

**Fig. 1** Functional Decomposition (Level-0)

Fig. 1 shows the level-0 top-down perspective of the NES FPGA; it consists of three main inputs and three main outputs, alongside being electrically powered. The power switch will allow the NES FPGA system to be powered on. Then, the user will input signals via buttons to select a program to load. The NES FPGA will run instructions to output both display and audio to the user, as well as system status LEDs to determine both battery and power status.

# 2.2 Function Decomposition (Level 1)

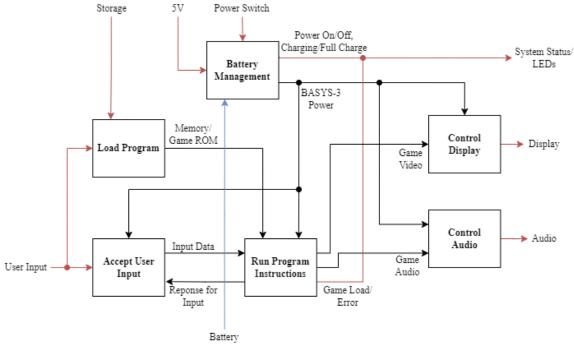

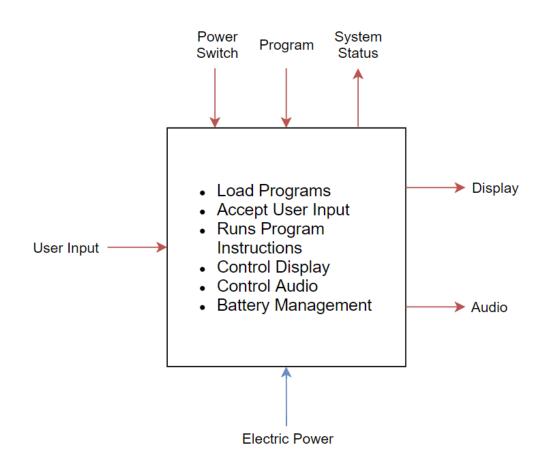

**Fig. 2** Functional Decomposition (Level-1)

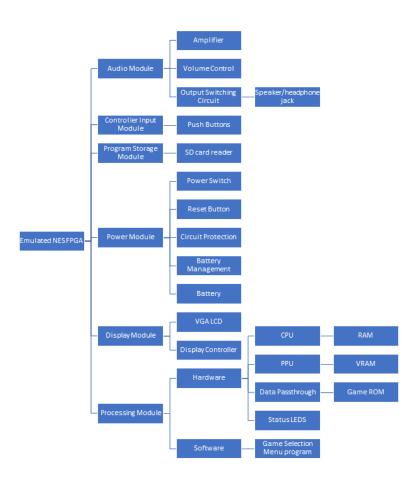

Fig 2 shows the level-1 Functional Decomposition diagram of the NES FPGA. There are five main modules: Accept User Input, Load Program, Battery Management, Run Program Instructions, Control Display, and Control Audio.

#### **2.3 Function Decomposition (Level 2)**

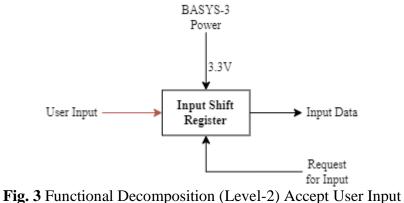

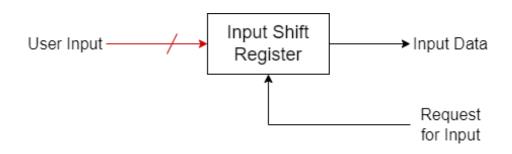

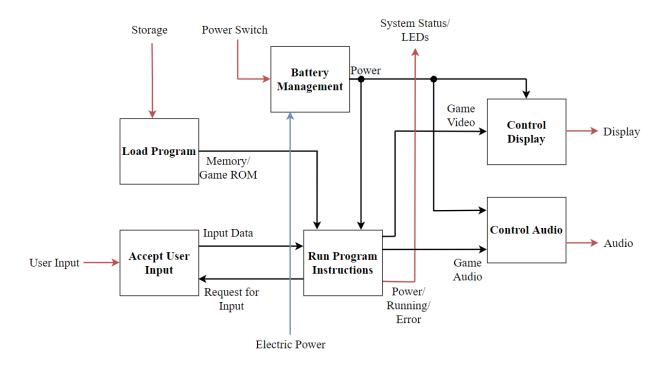

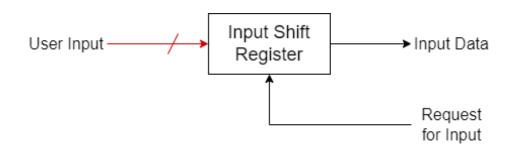

**Fig. 5** Functional Decomposition (Level-2) Accept User Input

Fig. 3 shows the level-2 diagram for the Accept User Input module. This function is based on the NES controller, which is composed of a single shift register. The user will input button signals to the shift register, which can be controlled by a request from the program. When the program requests for inputs via a clock signal, the shift register will send input data to the program.

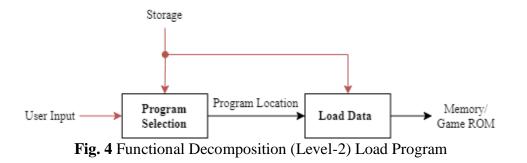

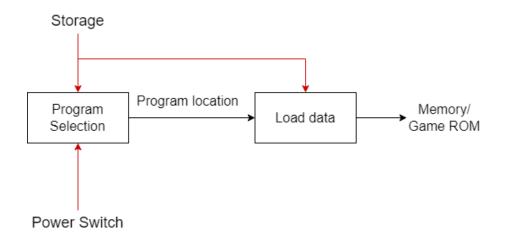

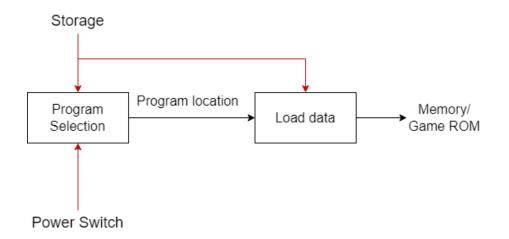

Fig. 4 shows the level-2 diagram for the Load Program module. Storage is an insertable SD card that is read by the FPGA through program selection and load data functions. The user will be able to select a program to run. The FPGA will take the location of the program and load it from storage.

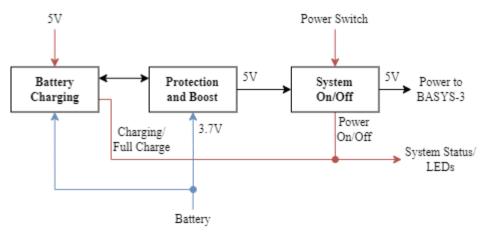

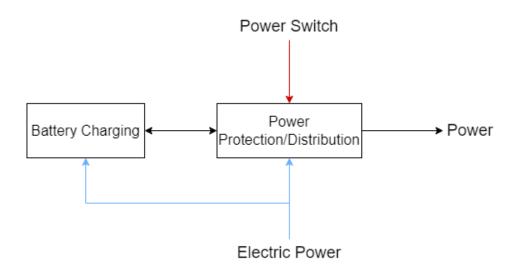

Fig. 5 Functional Decomposition (Level-2) Battery Management

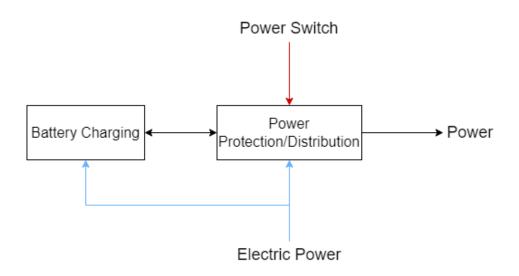

Fig. 5 shows the level-2 diagram for the Battery Management module. 5V of Electric power is sourced from a DC power supply which charges the battery. The battery distributes 3.7V, which is converted back to 5V to power the system.

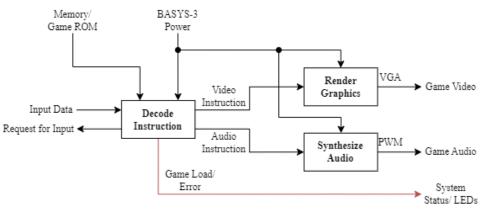

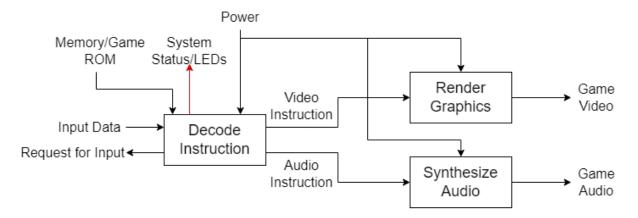

Fig. 6 Functional Decomposition (Level-2) Run Program Instructions

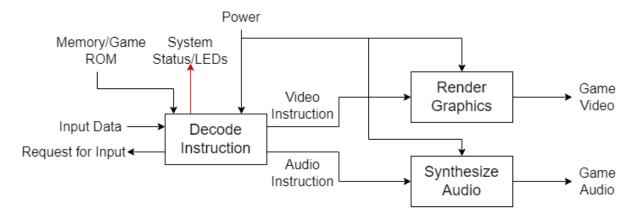

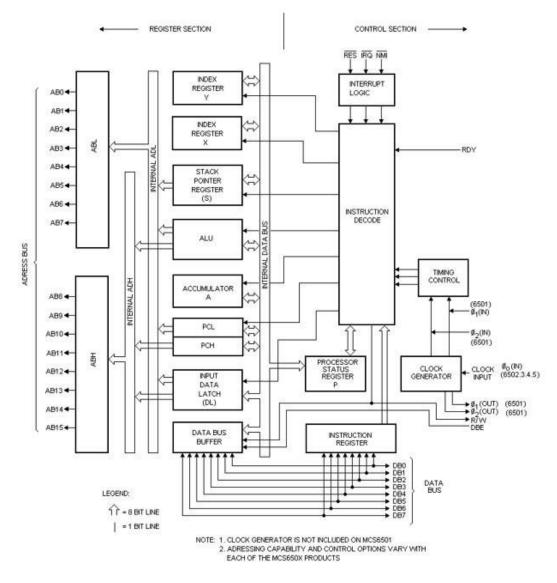

Fig. 6 shows the level-2 diagram for the Run Program Instructions module. This module represents all the inputs and outputs of the BASYS-3 board. The Decode Instructions, Render Graphics, and Synthesize Audio modules exist in the Verilog Code. The BASYS-3 is powered by 5V and receives input data from the user and the memory/game ROM from the SD card. The ROM is decoded and the FPGA renders graphics and synthesizes the audio.

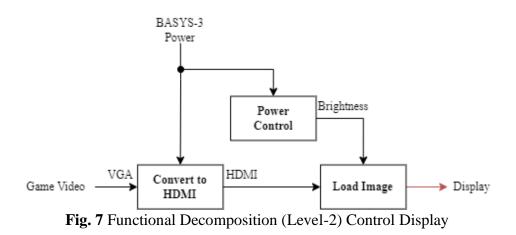

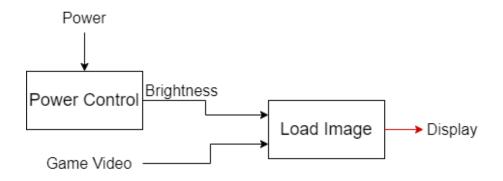

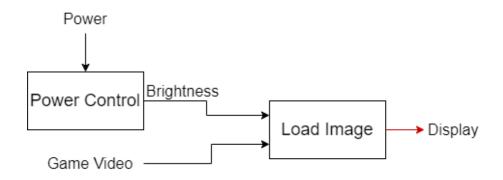

Fig. 7 shows the diagram for the Control Display module. The BASYS-3 outputs VGA signals, which is converted to HDMI signals. The LCD screen we chose requires an HDMI signal.

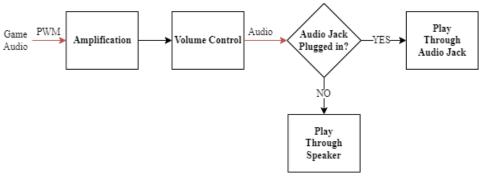

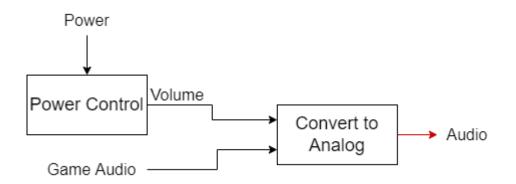

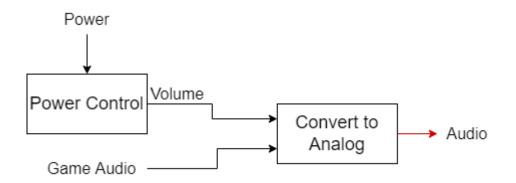

Fig. 8 Functional Decomposition (Level-2) Control Audio

Fig. 8 shows the diagram for the Control Audio module. The PWM audio signal is amplified by 12dB. The volume of this audio can then be adjusted by the user via a potentiometer. The audio jack will have switching functionality: if no device is plugged into the jack, the audio will play through the speaker; if a device is plugged into the jack, audio will play through the device.

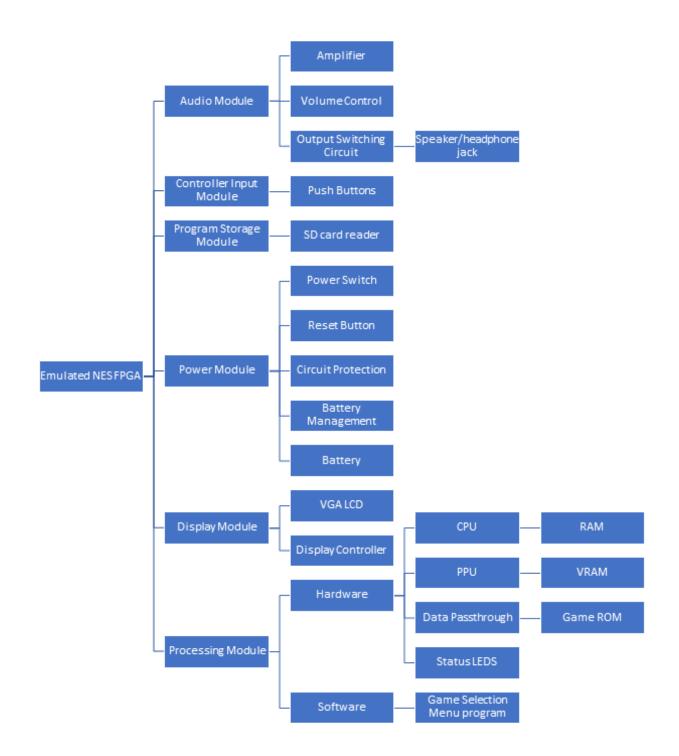

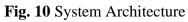

### 2.4 System Architecture

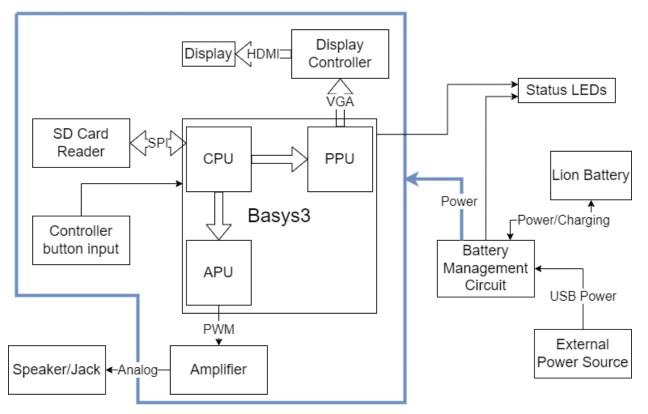

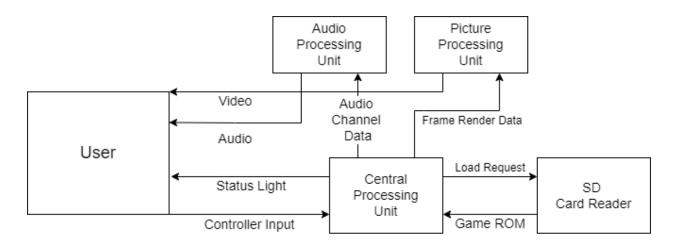

Fig. 9 System Architecture of FPGA NES device

Fig. 9 shows the System Architecture. The blue boxed modules are powered by the Battery Management Circuit module, which can charge a li-on battery via USB from an external power source. Within the BASYS-3 module are three sub-modules which are contained within the NES architecture: the Central Processing Unit (CPU), the Picture Processing Unit (PPU), and the Audio Processing Unit (APU).

## **2.5 Dataflow**

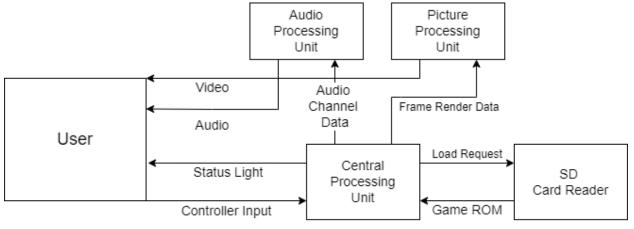

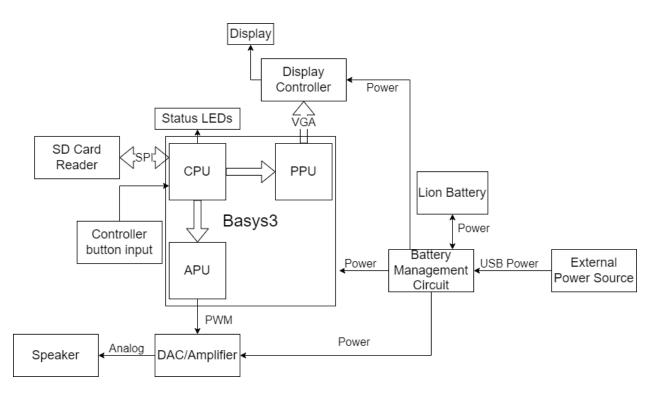

Fig. 10 Dataflow chart of FPGA NES device

Fig. 10 shows the Dataflow chart between the User and the device's modules. Observable data to the user are Video output, Audio output, and Status Lights from the FPGA NES device.

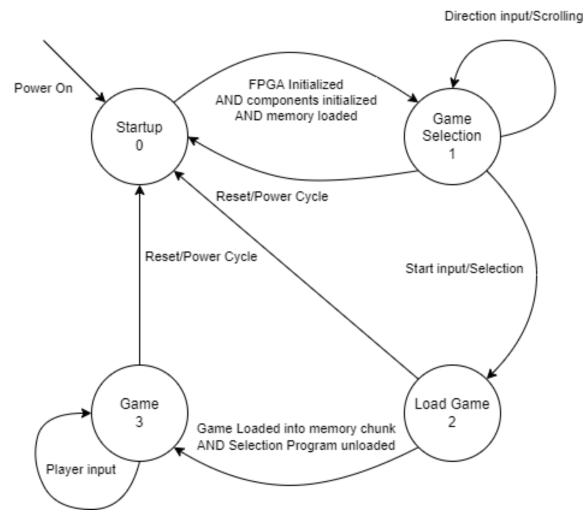

### 2.6 State Diagram

Direction input/Scrolling FPGA Initialized Power On AND components initialized AND memory loaded Game Startup Selection 0 1 Reset/Power Cycle Reset/Power Cycle Start input/Selection Load Game Game 3 2 Game Loaded into memory chunk AND Selection Program unloaded Player input

Fig. 11 State diagram of FPGA NES device

Fig. 11 Shows a state diagram of all the possible states the NES device will be in. The NES device will startup via a switch and initialize to a method for game selection. The user will choose the game to run by selecting it with button inputs. After choosing, the game will be loaded and start running, allowing the user to play the game.

### **2.7 Circuit Schematics**

#### 2.7.1 Controller

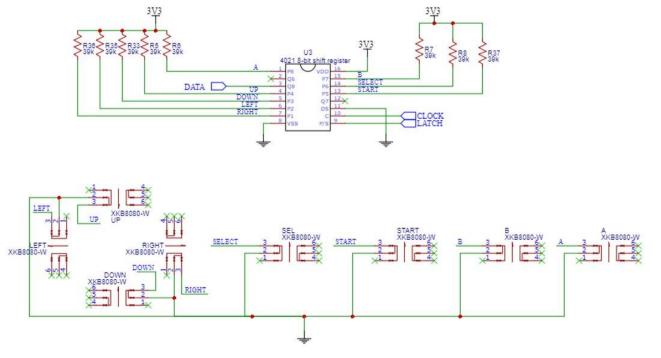

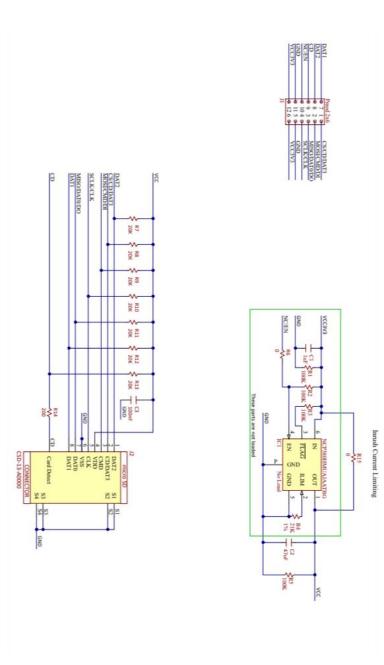

Fig. 12 Circuit Schematic of Controller

The original NES has eight buttons for user input and was referenced for our design [1]. The main IC that makes the controller work is a 4021 shift register that takes eight inputs from the eight buttons, a clock signal, and a latch signal. When the shift register receives the latch signal, it saves the state of all eight inputs. The clock signal then repeats 8 times to read all eight buttons. The recorded input is then sent out of the data pin to the FPGA to be interpreted while the corresponding actions are executed. The controller takes up half of one of the four PMOD ports.

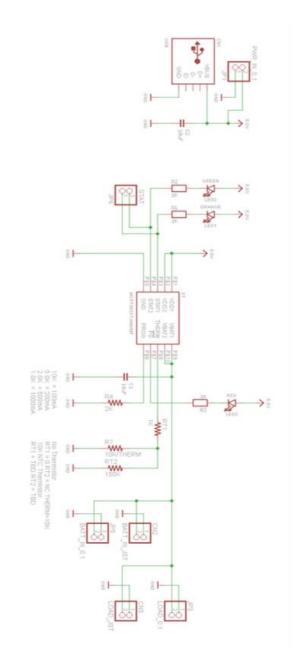

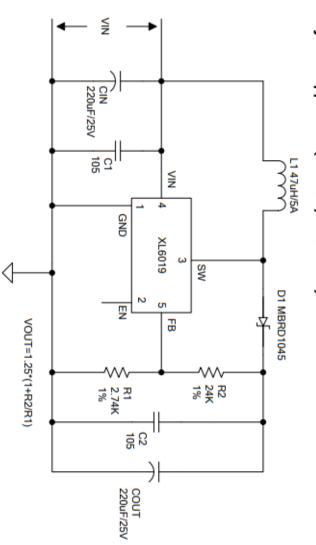

#### 2.7.2 Power/Charging

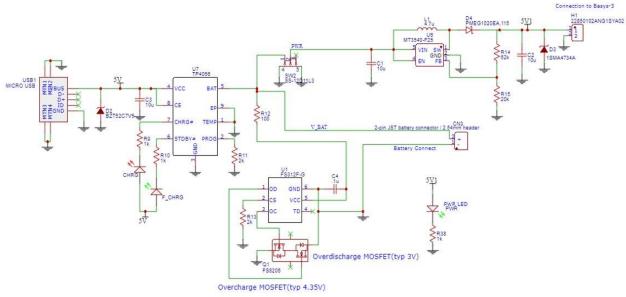

Fig. 13 Circuit Schematic of Power/Charging

In order to achieve portability of the system, a battery needed to be included. The battery is connected to a 5V boost converter in order to supply power to the BASYS-3. A charger IC is also connected so that once an external 5V source is connected, the battery will be able to recharge when needed. There are status LEDs that show when the battery is charging and when the battery is fully charged. Additionally, a protection IC is included so that the battery will not reach a state of overcharge or over discharge. Schottky diodes are included on the main power lines so that if there are any spikes in voltage the connected components will not be damaged.

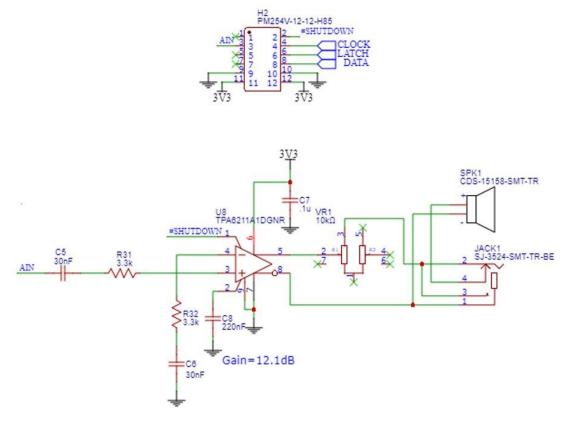

#### 2.7.3 Audio

Fig. 14 Circuit Schematic of Audio

The audio that comes out of the BASYS-3 is a PWM signal that is sent through an audio amplifier which applies a gain of 12.1 dB. Once the signal is amplified, the user has the option to control the volume via a potentiometer. There are two different destinations for the audio once the volume is set: the first being the default speaker that is on-board; the second option is when the user plugs a device into the 3.5mm audio jack and the audio will automatically switch over to that device. The audio module takes up the other half of the PMOD port that the controller uses.

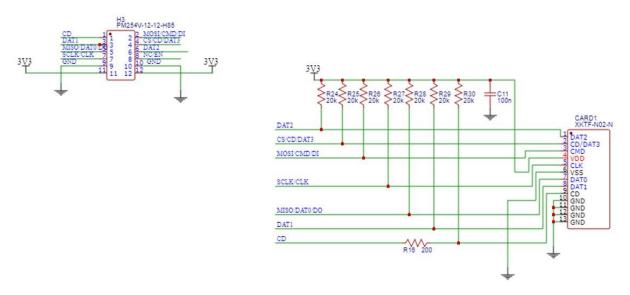

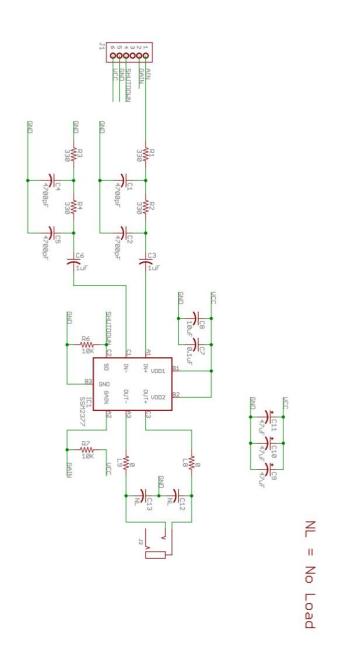

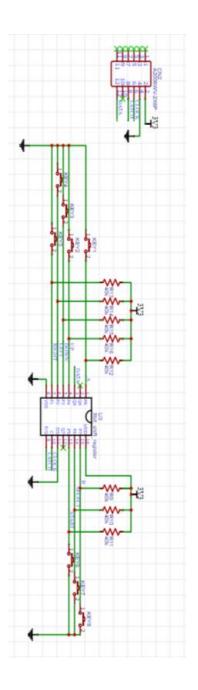

## 2.7.4 Memory

Fig. 15 Circuit Schematic of Memory

This circuit is simply a breakout for the SD card slot. Each signal is pulled high via a 20k resistor. The logic for this module is handled on the FPGA. The memory module takes up an entire PMOD port.

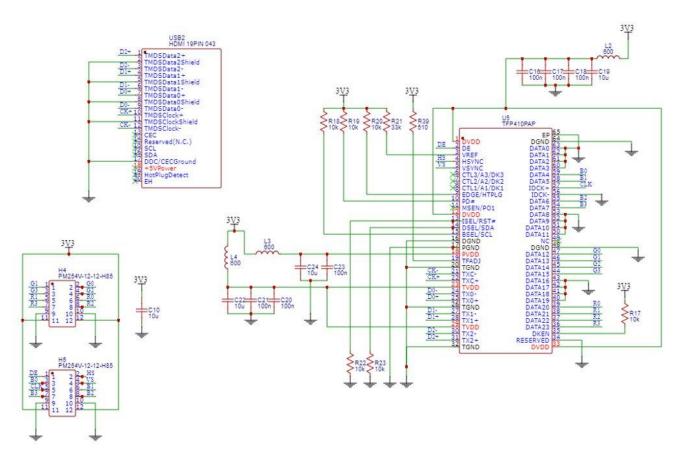

#### 2.7.5 Display

Fig. 16 Circuit Schematic of Display

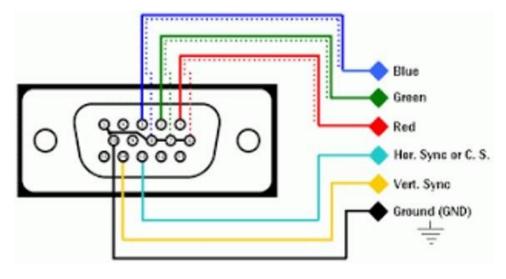

In order to display onto the LCD, we needed to convert the native VGA signal on the BASYS-3 to a digital signal. This was done using the TFP410PAP IC from Texas Instruments. There is also another IC from Lattice Semi called the SII164 that can be used if the TI chip is unavailable. These ICs take in the red, blue, and green signals along with horizontal and vertical sync and a clock signal to convert to the differential pair signals that works with the LCD's HDMI interface. This digital signal is then connected to a female HDMI port and a male-to-male HDMI ribbon cable is used to connect the PCB to the LCD. The display module takes up the two remaining PMOD ports on the BASYS-3.

#### 2.8 Software

#### 2.8.1 Rebuild

In order to use the open-source implementation of the NES from Brian Bennett we had to fix and modify the Verilog to get it running on the BASYS-3. One of the issues was that of constraints; the board used by Bennet was the Nexys-6 with a Spartan 6 FPGA [3]. Modifying constraints was trivial because the BASYS-3 had most of the I/O that the Nexys-6 had. One difference was that Bennett was using a breakout board for the NES Joypad controller [3]. This meant that we had to use the PMOD slots on the BASYS-3 directly. Bennett's project didn't make use for all the VGA color channels and so we modified the Verilog to include those on the BASYS-3 [3].

#### 2.8.2 Start Menu

The start menu is implemented using VGA and consists of a module for the generation of all the sync signals for the Vertical and Horizontal axis. This module is also responsible for generating the Pixel Clock and Enable signal. In order to display characters, we made a module for text generation that included a BRAM of ASCII characters. The X and Y axis sync signals were used to access the BRAM, this resulted in a text tile size of 80x30 characters. The start menu also includes a module to use the Joypad controller. This module is separate from the module used in the NES implementation because of clock domain issues. The result of these modules is a start screen of 9 Save game states that can be chosen with the joypad using the UP

and DOWN buttons and selected with the A button. The start screen was then multiplexed with the NES Implementation so that the start screen is initialized on boot-up.

|                | WHE SLOT 1  |  |  |

|----------------|-------------|--|--|

| •              | WHE SLOT 2  |  |  |

| •              | WHE SLOT 3  |  |  |

| •              | WHE SLOT 4  |  |  |

|                | GAME SLOT 5 |  |  |

|                | WHE SLOT 6  |  |  |

| i and          | GAME SLOT 7 |  |  |

|                | GAME SLOT 8 |  |  |

| 1 18           | GAME SLOT 9 |  |  |

| Independent of |             |  |  |

Fig. 17 Game selection menu

2.8.3 Game Storage

Nesdev Wiki provided a plethora of information on programming topics for the NES [4]. It

was used when we development started for a game selection menu and for changing memory

map values accordingly to each game stored on the SD card.

# 2.9 Hardware

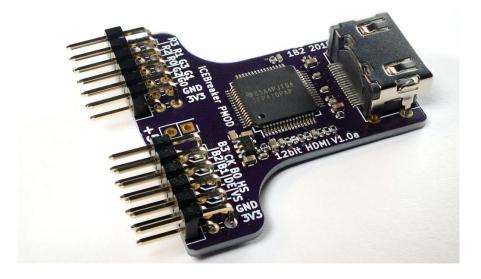

#### 2.9.1 VGA to HDMI

Fig. 18 VGA to HDMI converter PMOD

We based our display circuitry on the PMOD Digital Video Interface by 1BitSquared [2]. It uses two PMOD ports and converts the VGA signal from the BASYS-3 to an HDMI signal.

#### 2.9.2 SD Card

Fig. 19 MicroSD card reader PMOD

We based our memory circuitry on the MicroSD Card Slot by Diligent, a simple breakout board for the MicroSD card.

### 2.9.3 BASYS-3

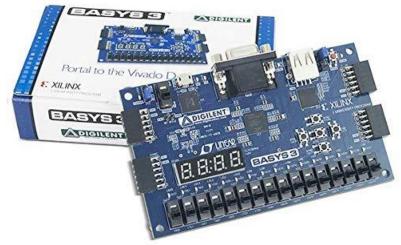

Fig. 20 BASYS-3 FPGA board

Our project revolves around the use of the BASYS-3, an FPGA prototyping board that all CEC Students have at GMU. The BASYS-3 holds the NES CPU architecture and will handle all input and output signals.

# 2.9.4 Display

Fig. 21 HDMI 5" Display Backpack

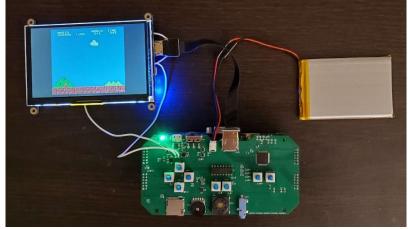

We chose to have an HDMI 5" display backpack. The NES architecture outputs VGA signal, therefore in the display circuit on the PCB, the VGA signal is converted to HDMI by a TFP410PAP IC.

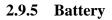

Fig. 22 3.7V 4000mAh Li-ion Rechargeable Battery

We used a 3.7V 4000mAh Li-Po rechargeable battery to power our project. Within the PCB circuit, the battery power is boosted to 5V in order to power the BASYS-3.

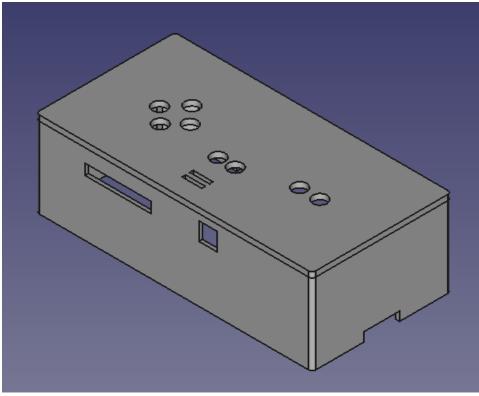

2.9.6 PCB

Fig. 23 PCB containing all necessary circuits

The PCB was designed in EasyEDA software and manufactured by JLCPCB. We designed the PCB to contain all necessary circuits needed for controller, power management/ charging, audio, SD card memory, and display output. To interface on top of the BASYS-3, we integrated PMOD headers on bottom of the PCB.

#### 2.9.7 CAD

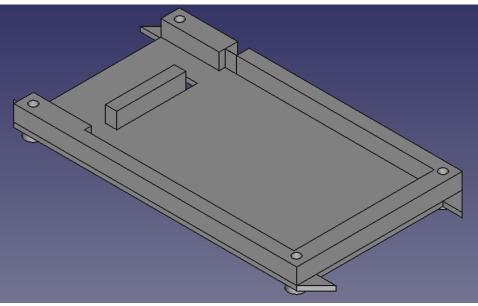

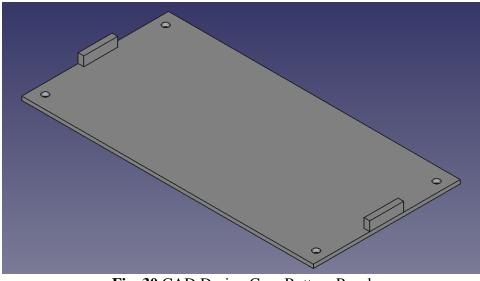

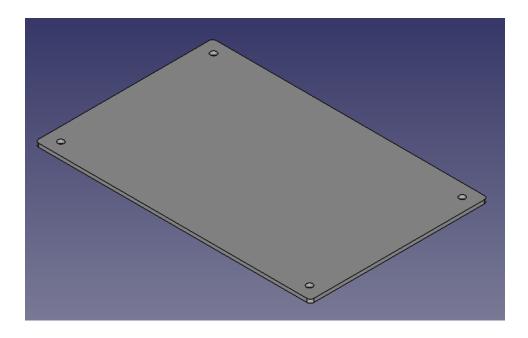

CAD design was conducted in FreeCAD software and printed in The Mason Exchange (The MIX) located in Horizon Hall at George Mason University. CAD design was alongside PCB design in order to create a case that would enclose the manufactured PCB and other component as well as leave openings for the user to handle such as the potentiometer for volume control, audio jack, and ports from the BASYS-3 and PCB.

#### 2.9.7.1 3D Models

Fig. 24 CAD Design Top Screen Front Panel

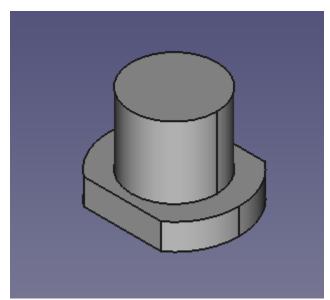

Fig. 25 CAD Design Button

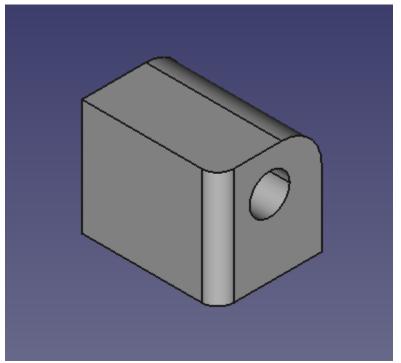

Fig. 26 CAD Design Hinge

Fig. 27 CAD Design Bottom Case

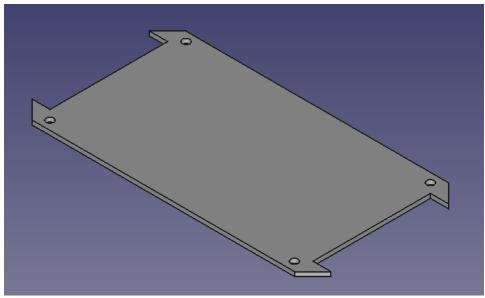

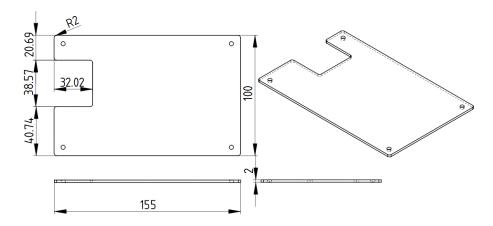

Fig. 28 CAD Design Internal Plate 2

Fig. 29 CAD Design Internal Plate 1 (Battery Hold)

Fig. 30 CAD Design Case Bottom Panel

Fig. 31 CAD Design Top Screen Back Panel

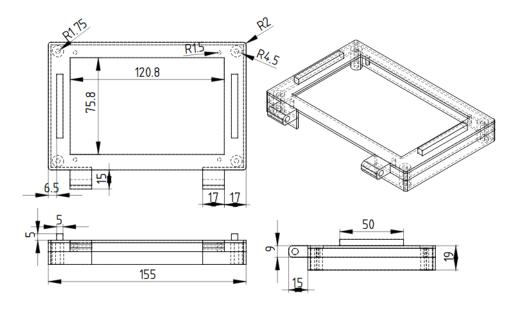

# 2.9.7.2 Orthographic Projections (mm)

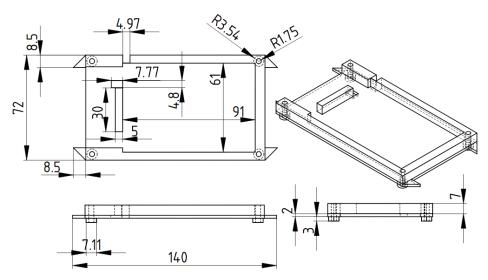

Fig. 32 CAD Design Top Screen Front Panel Orthographic Projection (mm)

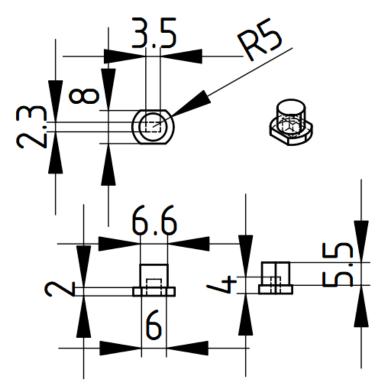

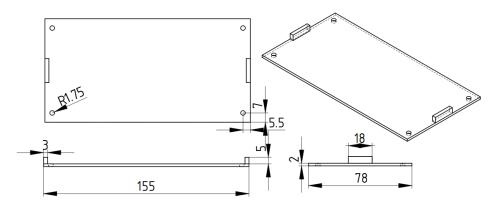

Fig. 33 CAD Design Button Orthographic Projection (mm)

Fig. 34 CAD Design CAD Design Hinge Orthographic Projection (mm)

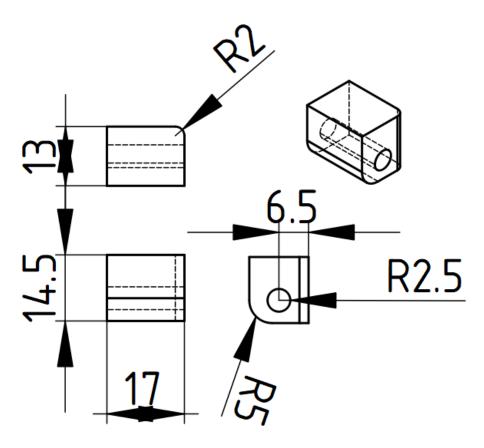

Fig. 35 CAD Design Bottom Case Orthographic Projection (mm)

Fig. 36 CAD Design Internal Plate 2 Orthographic Projection (mm)

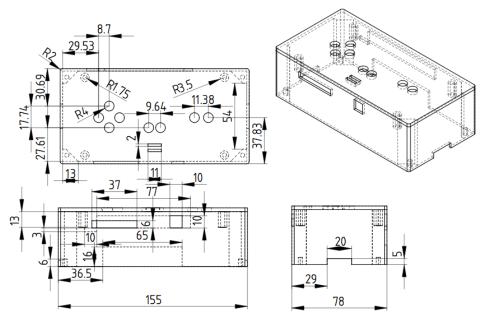

Fig. 37 CAD Design Internal Plate 1 (Battery Hold) Orthographic Projection (mm)

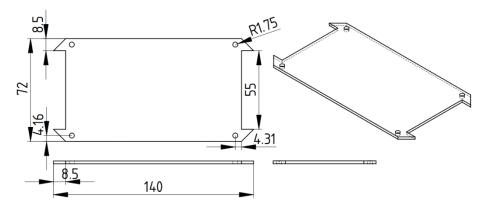

Fig. 38 CAD Design Case Bottom Panel Orthographic Projection (mm)

Fig. 39 CAD Design Top Screen Back Panel Orthographic Projection (mm)

## 2.9.7.3 3D Print Results

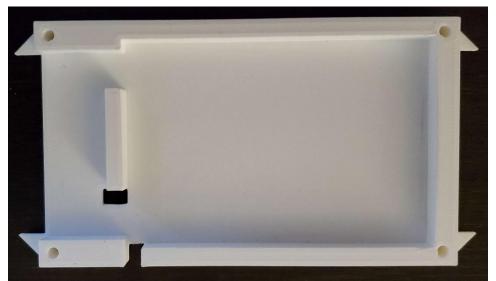

Fig. 40 CAD Design Top Screen Front Panel 3D Print

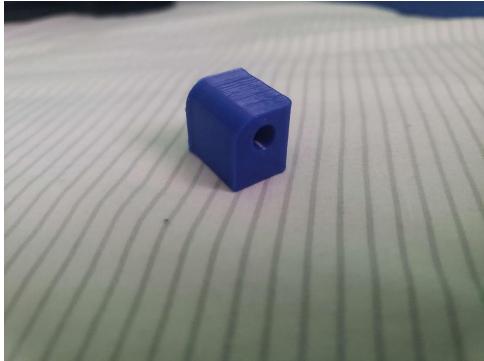

Fig. 41 CAD Design Button 3D Print

Fig. 42 CAD Design Hinge 3D Print

Fig. 43 CAD Design Bottom Case 3D Print

Fig. 44 CAD Design Internal Plate 2 3D Print

Fig. 45 CAD Design Internal Plate 1 (Battery Hold) 3D Print

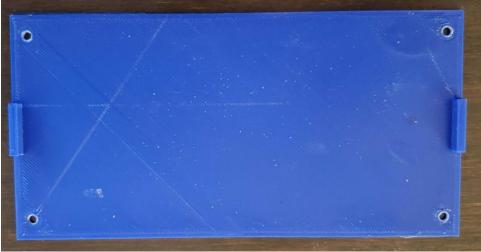

Fig. 46 CAD Design Case Bottom Panel 3D Print 3D Print

Fig. 47 CAD Design Top Screen Back Panel 3D Print

# **3. Experimentation**

## **3.1 Introduction**

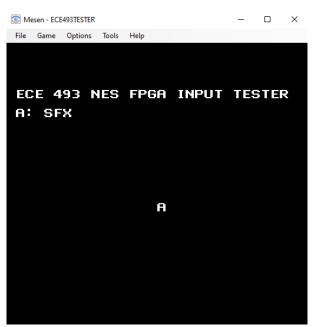

Three experiments were conducted to confirm the playability and the portability of our NES FPGA device: Audio and Video Synchronization, Button Response Time, and Battery Lifetime on Full Charge. The success of these experiments was crucial to the user experience needed to use our NES FPGA device. Before we could measure latency experiments, we first decided to create our own NES "game", named ECE493TESTER (Fig. 48), for testing purposes only; it is essentially for display button inputs on screen and for playing a sound when a button is pressed. Nesdoug's tutorial on coding an NES game was used for our testing program [5].

Fig. 48 The ECE493TESTER running on the Mesen Emulator while pressing the button A

### 3.2 Audio and Video Synchronization

### **3.2.1** Experiment Introduction

The goal of this experiment was to measure the latency between audio and video. In other words, we wanted to observe if audio cues from a game match up with the actions in-game that cause the audio.

#### 3.2.2 Results

We decided to collect data of the audio and video by human observation, and we concluded that at the human level, the audio and the video are synchronized with an undetectable latency. We also observed that the quality of the audio speaker was subpar. Incorrect filtering or speaker component choice are factors that could affect the sound quality.

## **3.3 Button Response Time**

### **3.3.1** Experiment Introduction

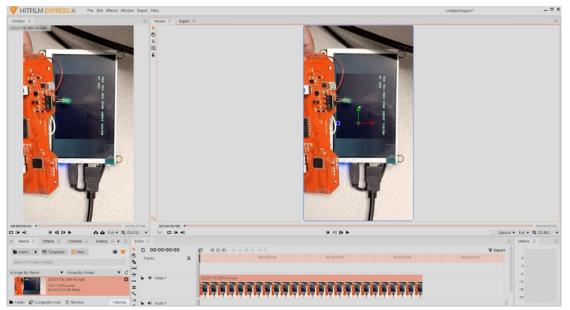

Fig. 49 The video recording was analyzed within HitFilm

The goal of this experiment was to measure the response time between a button press and an on-screen response. To take the measurements, we used a Samsung S10 smartphone with 960 fps and viewed the video in HitFilm, a video editing software (Fig. 49). The number of frames were counted in between, then the response time was calculated:

$$\frac{1}{960 \, frame/second} = 1.04 \, ms/frame$$

| Response Time = | $CountedFrames$ $\cdot$ | 1.04 ms/ | frame |

|-----------------|-------------------------|----------|-------|

|-----------------|-------------------------|----------|-------|

#### 3.3.2 Results

|                    | P1                 | R1   | P2   | R2 |  |  |

|--------------------|--------------------|------|------|----|--|--|

| Counted Frames     | 85                 | 87   | 85   | 75 |  |  |

| Response Time (ms) | 88.4               | 90.4 | 88.4 | 78 |  |  |

| P: Press           | Average = 86.32 ms |      |      |    |  |  |

| R: Release         |                    |      |      |    |  |  |

Table 1 Measurements of frame data

## 3.4 Battery Lifetime on Full Charge

#### 3.4.1 Experiment Introduction

Fig. 50 Super Mario Bros. being played on the NES FPGA

The goal of this experiment was to test and compare our theoretical calculations of the battery life with experimental results of our measured battery life. We set up the experiment by loading the ROM for Super Mario Bros. and starting the game. In the game, Mario has about 2 minutes and 40 seconds to complete a level; when the time runs out, Mario loses a life. Since Mario only has 3 lives, the level needed to be manually reset every 8-10 minutes. This process was repeated until the NES FPGA lost power.

#### 3.4.2 Results

After 3 hours and 3 minutes, the NES FPGA started to lose power to the display. Our initial battery life calculations gave us an estimated battery life of 3.36 hours:

LCD Watts + Speaker Watts + FPGA Watts

Our experimental results yielded 10% less battery life than we had expected.

## 4. Experiment Validation

We had collected data on how our system performed but it was also important to validate our system qualitatively. We wanted our project to be as close to the real NES as possible in order to make sure that the user would get the same experience. The process for validating these results was relatively simple, we played Super Mario on the console and made sure to check for any input latency issues, display issues, or audio latency issues. This validation resulted in us concluding that the device offers an acceptably similar experience to the original NES.

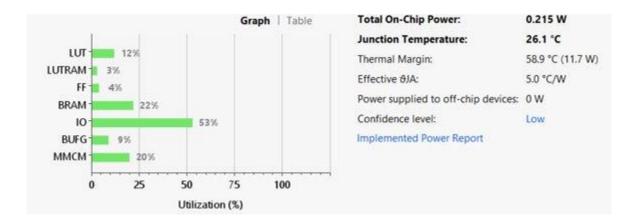

The goal of this project was to provide a platform on which other systems can be emulated. We had to take careful account of how we used our FPGA's resources in order to allow growth. From Fig. 51, we have a very large margin for growth. Our only real limiting resource would be IO, but the amount of IO needed would remain relatively constant across platforms unless we decided to emulate something far more modern than the NES or SNES.

Fig. 51 Utilization graph for FPGA

## **5.** Project Lifetime

## 5.1 Maintainability/Maintenance of Final Design

The end user should have little maintenance when it comes to just using the device. The user may have to replace buttons as they wear down or replace the battery as it degrades. The overall casing that houses the system should be able to last a long time, though if necessary, it too can be replaced if the user has access to the 3D model stl file. We expect the electrical components such as the display, Basys-3, and PCB to last throughout the product's lifetime.

## 5.2 End of Project's Lifetime

All parts and components used in this project are easily sourced via electronic suppliers and it is quite unlikely that any given parts will reach the end of their lifetime and stop being manufactured. Moreover, all the parts used have standard alternatives that the user can easily substitute in place of our chosen components. When it comes to disposing of the device it is considered E-waste because of the battery so this means the user must dispose of it correctly. While the constructed project is able disposed of at the end of its "lifetime," this project is capable of being replicated and improved upon should another choose to do so, so this project does not truly have an end.

## 6. Administration

#### **6.1 Progress**

With the start of ECE 492, we went through our planning and design process for the project. We touched on topics of how the device should visually look and what functionalities it should have. We then came up with solutions to solve our problem statement. In ECE 492, we conducted part selection after we finalized our design. This included searching for parts for the display, audio, battery, and storage. We did some preliminary work on schematic capture for the circuits, which also included prototypes of our controller and audio circuits via breadboards. We also explored some solutions for storing the game ROMs in memory.

During ECE 493, we started on the schematic capture and layout for the PCB that would mount onto the BASYS-3. Alongside the development of the PCB, we started work on the CAD enclosure that would house the BASYS-3, battery, display, and PCB systems, as well as the wires that connect them. The manufactured PCB we designed took two iterations with a few changes done in-between before it was properly functional. The CAD enclosure went through several different iterations, featuring various designs and implementations for each part. We also started writing the RTL for the storage and attempting to save game ROMs onto the SD Card. The RTL was written for the VGA-HDMI converter and for the start menu screen. We ran into issues with saving game ROMs onto the SD Card and were not able to complete that functionality by the end of ECE 493.

### 6.2 Changes to Design

We had to make several changes to the design especially for the design concerning memory storage of the video game ROMs. Starting out the goal was to use the 6502 core inside the NES implementation to run software that would load the ROMs that the user wanted to play. We decided to not pursue this design and instead opted for a Verilog implementation of a start menu. The start menu works by being the first screen that the user sees when the device is powered on. In the start menu, the user will be able to choose the game to play. This is opposed to the software approach where this start menu would've been entirely in software ran by the 6502 core.

When deciding on how to get our video signal to the LCD, we initially were going to use a ZIF connector on the PCB so that we could use a ribbon cable coming out of the case to take up less space. In order to do that we would have had to use a ZIF to HDMI converter PCB to connect to the LCD. We thought this was not the best solution, so we decided on replacing the ZIF connector on the PCB with a female HDMI and finding a ribbon cable HDMI cord to get the signal to the LCD.

During the circuit design process there were multiple other times where a component was unavailable or not what we needed/wanted. In our audio module we ran into a problem where the chip we wanted to use was out of stock and the only one we had was a very small BGA configuration so we were not confident that we could solder it onto our PCB without damaging the board or creating a short. This issue led us to find another mono-channel audio amplifier that would have an adjustable gain and not consume too much power. Another circuit design issue was the display module. When looking for a solution to make our display portable, we had to look to VGA to HDMI conversion because we could not find a small enough VGA screen. To do this we started by breaking open a cheap VGA to HDMI converter cable and seeing what was inside. After doing that we ran into the problem of not being able to obtain the required chip and its datasheet to know if we were hooking it up correctly or not. Finally, after some more searching and research we were able to find a company that had previously done VGA to HDMI conversion through PMOD and decided to recreate it so it would work with the BASYS-3.

One of our design choices was about determining the physical design or construction of the device. Originally, we went with a single block design, where the controls and screen were on the same face of the case. This would have meant our PCB design would have had to been changed to support both the buttons and display next to each other. We opted to go for a display that is hinged and allows us to close the display. This would have also affected how much filament we would use and how we designed the daughter board, however the effects and impacts of using this design are unknown.

A design choice involving the display was either using an adapter cable for VGA to HDMI or using a chip specially made for converting VGA to HDMI. We opted to go for the chip specially made for this situation. This allowed us to place it on the PCB and save space inside the case of the device. The adapter on the other hand was bulky, unwieldy and too complicated to power inside the case.

## **6.3 Unplanned Activities**

We faced a variety of obstacles through the duration of this project. One of the more impactful obstacles was sourcing the PCB and the components itself. Ordering parts that originate from a different country proved to take longer than we thought, and the shipping is unreliable.

# 6.4 Funds Spent

|         |          |                                                                                                                    |       | Cost        | Shippi |      |        |        |                      |

|---------|----------|--------------------------------------------------------------------------------------------------------------------|-------|-------------|--------|------|--------|--------|----------------------|

| Buyer   | Quantity | Part                                                                                                               | Cost  | w/ Quantity | ng     | Tax  | Total  | Cumu   | lative Cost          |

|         |          |                                                                                                                    |       |             |        |      |        |        | Total<br>w/o shippin |

| Amilcar | 1        | P-MOD Audio Amp                                                                                                    | 9.99  | 9.99        | 4.99   | 0.6  | 25.57  | Total  | g and tax            |

| Anthony | 1        | P-MOD MicroSD                                                                                                      | 6.99  | 6.99        | 0      | 0    | 6.99   | 547.97 | 428.61               |

| Josh    | 1        | P-MOD MicroSD                                                                                                      | 6.99  | 6.99        | 9.99   | 0    | 16.98  |        |                      |

| Sam     | 1        | P-MOD MicroSD                                                                                                      | 5.94  | 5.94        | 0      | 0    | 5.94   |        |                      |

| Brooks  | 1        | NES Controller<br>(Potted)                                                                                         | 7.79  | 7.79        | 0.47   | 0    | 8.26   |        |                      |

| Brooks  | 1        | NES<br>Controller (Genuine)                                                                                        | 8.98  | 8.98        | 4.89   | 0    | 13.87  |        |                      |

| Sam     | 1        | Lithium Battery<br>3.7v 4000mah                                                                                    | 13.99 | 13.99       | 0      | 0.88 | 14.87  |        |                      |

| Sam     | 1        | Digital Caliper                                                                                                    | 8.99  | 8.99        | 0      | 1.56 | 10.55  |        |                      |

| Sam     | 1        | VGA to HDMI                                                                                                        | 16.99 | 16.99       | 0      | 0    | 16.99  |        |                      |

| Sam     | 1        | Adafruit Lipoly Charger                                                                                            | 12.5  | 12.5        | 0      | 0    | 12.5   |        |                      |

| Sam     | 1        | 3pcs DC to DC<br>booster                                                                                           | 9.99  | 9.99        | 0      | 0.6  | 10.59  |        |                      |

| Brooks  | 1        | VGA to HDMI                                                                                                        | 17.99 | 17.99       | 0      | 0.95 | 18.94  |        |                      |

| Brooks  | 1        | Controller<br>Components                                                                                           | 1.87  | 1.87        | 8.82   | 0    | 10.69  |        |                      |

| Brooks  | 1        | VGA-<br>hdmi components                                                                                            | 1.48  | 1.48        | 8.54   | 0    | 10.02  |        |                      |

| Brooks  | 1        | VGA-hdmi chips                                                                                                     | 17.56 | 17.56       | 6      | 1.05 | 24.61  |        |                      |

| Josh    | 2        |                                                                                                                    | 19.45 | 38.9        | 7      | 0    | 52.9   |        |                      |

| Sam     | 1        | 3 inch embedded display                                                                                            | 37.99 | 37.99       | 0      | 6    | 43.99  |        |                      |

| Anthony |          | HATCHBOX<br>1.75mm True Blue<br>PLA 3D Printer<br>Filament, 1 KG Spool,<br>Dimensional Accuracy<br>+/- 0.03 mm, 3D | 24.99 | 49.98       | 0      | 1 5  | 52.98  |        |                      |

| Brooks  |          | Ū                                                                                                                  | 93.75 | 93.75       |        |      | 113.76 |        |                      |

| Sam     |          | · · ·                                                                                                              | 59.95 | 59.95       |        |      | 76.97  |        |                      |

|         |          | Table 2 Total funda                                                                                                | 50.00 | during ECE  |        | ECE  |        |        |                      |

**Table 2** Total funds spent during ECE 492 and ECE 493

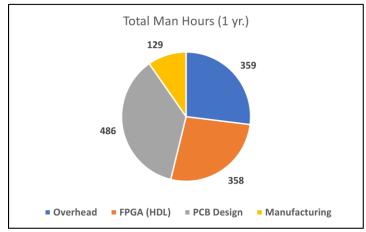

## 6.5 Man-hours Spent

| Task                       | <u>Sam</u> | <u>Josh</u> | <u>Anthony</u> | <u>Amilcar</u> | <u>Brooks</u> | <u>Total</u> |

|----------------------------|------------|-------------|----------------|----------------|---------------|--------------|

| Overhead                   | 53         | 40          | 40             | 44             | 40            | 217          |

| Storage                    | 90         | 15          | 0              | 0              | 0             | 105          |

| Video                      | 20         | 73          | 0              | 0              | 0             | 93           |

| Rebuild                    | 80         | 80          | 0              | 0              | 0             | 160          |

| Circuit                    | 0          | 0           | 20             | 36             | 130           | 186          |

| PCB                        | 0          | 0           | 4              | 56             | 25            | 85           |

| Case                       | 2          | 0           | 57             | 6              | 2             | 67           |

| Documentation              | 15         | 12          | 20             | 80             | 15            | 142          |

| Testing                    | 19         | 19          | 10             | 15             | 5             | 68           |

| Manufacturing<br>Component | 0          | 0           | 62             | 0              | 0             | 62           |

| Research                   | 10         | 10          | 10             | 10             | 40            | 80           |

| Total Hours/Person         | 289        | 249         | 223            | 247            | 257           | 1265         |

Table 3 Hours each person spent on tasks

| Division      | <u>Sam</u> | <u>Josh</u> | Anthony | <u>Amilcar</u> | <u>Brooks</u> | <u>Total</u> |

|---------------|------------|-------------|---------|----------------|---------------|--------------|

| Overhead      | 68         | 52          | 60      | 124            | 55            | 359          |

| FPGA (HDL)    | 190        | 168         | 0       | 0              | 0             | 358          |

| PCB Design    | 31         | 29          | 101     | 123            | 202           | 486          |

| Manufacturing | 2          | 0           | 119     | 6              | 2             | 129          |

## Table 4 Hours each person spent on division

Fig. 52 Chart of total man-hours spent on our project in ECE 492 and ECE 493

## 7. Lessons learned

### 7.1 Skills

Time management was essential for the project. During ECE 492 and ECE 493, there were many moments where we would be behind our intended schedule and had to work harder as a result to catch up with our plans. Teamwork was another group skill that we worked through and improve as the year passed. As our members were split into sub-sections, we worked together as each group coordinated with each other as progress was made. Finally, we worked on our documentation skills as we prepared for proposals, progress reports, and presentations throughout the year. There were some challenges with document formatting, providing correct and necessary information, and making our work professional to be given to our faculty supervisor for review.

### 7.2 Knowledge

#### 7.2.1 Verilog

During this project, we had to learn many different skills. One of the skills we had to learn, in which we had no prior exposure to, was the Verilog HDL. The original NES implementation was entirely in Verilog, and converting such a project to VHDL, a language we had learned in our GMU courses, was unfeasible. We decided on learning Verilog HDL and implementing our solution entirely in Verilog HDL.

#### 7.2.2 PCB Design

During the process of designing the PCB, we learned how to fit all necessary components onto the PCB with a predefined amount of space and only two layers to work with. The use of vias and copper areas helped with these limitations. Also, having to find different components that take up less space also helped.

#### 7.2.3 6502 Architecture

#### 7.2.4 CAD Design

During ECE 493, alongside the PCB design, we had to learn to design, model, and print an enclosure for our system. The main goal was to design an enclosure that would be able to fit all the components we chose for our project and still be a manageable size to be handled. Measurements were carefully taken to allow the PCB design and 3D prints to fit smoothly together and allow the necessary parts such as audio jack and potentiometer be accessible to the user.

# 8. References

- [1] Bob, "How a NES controller works," RetroRGB, 7 March 2020. [Online]. Available: https://www.retrorgb.com/how-a-nes-controller-works.html. [Accessed 29 November 2022].

- [2] Esden, "PMOD Digital Video Interface," 1BitSquared, [Online]. Available: https://1bitsquared.com/products/pmod-digital-video-interface. [Accessed 3 December 2022].

- [3] B. Bennett, "FPGA-based Nintendo Entertainment System Emulator," 14 July 2012. [Online]. Available: https://github.com/brianbennett/fpga\_nes. [Accessed 2022].

- [4] "NesDev Wiki," 22 July 2022. [Online]. Available: https://www.nesdev.org/wiki/Nesdev\_Wiki. [Accessed 2022].

- [5] Dougeff, "How to Program an NES game in C," 2 January 2022. [Online]. Available: https://nesdoug.com/. [Accessed 2022].

# 9. Appendix A: Proposal (ECE-492) ECE-492 PROPOSAL

# NES handheld emulation breakout board for the BASYS-3

Team Members: Joshua Thomas Riggs, Brooks Aaron Corbett, Anthony Thinh Tang, Samuel Kifle Kebadu, Amilcar Alejandro Paniagua

Date of Submission: 3/11/2022

Faculty Supervisor: Dr. Jens-Peter Kaps

## **Executive Summary**

Options for Nintendo Entertainment System (NES) emulation are limited with the requirements of being portable and hardware emulated. Our solution is to design a breakout board with necessary interfaces and inputs/outputs, design an encasing for the purpose of being portable/handheld, and include cost effective components such as the LCD screen, battery, SD card, and audio speaker. This project will result in allowing the BASYS-3 to be a new platform for NES emulation and in providing a new option for DIY NES emulation. Our team is composed of five members, majoring in Computer Engineering and Electrical Engineering:

| Team Member              | Relevant Experience  | Skills                       |

|--------------------------|----------------------|------------------------------|

| Samuel Kebadu (CpE) (PM) | ECE 447, 448         | Verilog, VHDL, C++, C,       |

|                          | FPGA Internship      | Computer Architecture        |

| Amilcar Paniagua (CpE)   | ECE 286, 447, 448    | VHDL, C++, C, Circuit        |

|                          |                      | Design, Soldering            |

| Brooks Corbett (EE)      | ECE 286, 447         | Circuit Design, PCBA         |

|                          | Hardware Engineering | Design, Power system design, |

|                          | Internship           | Soldering                    |

| Joshua Riggs (EE)        | ECE 448, 445, 436    | VHDL, Digital Design, PCB    |

|                          |                      | Design                       |

| Anthony Tang (EE)        | ECE 286, 445, 447    | AutoCAD, Circuit Design,     |

|                          |                      | Soldering, C                 |

## **Problem Statement**

NES emulation can vary in range of prices, with each method containing their advantages and disadvantages. We are motivated to seek a more cost-effective method for hardware emulating the NES in a portable package, meant to be hand-operated with a self-contained power source. We are also motivated to bring a new option for NES emulation with the BASYS-3.

As of Q1 2022, original NES home consoles can only be obtained secondhand. The most convenient method to play an NES is emulation by software. However, software emulation runs

on personal computers with general architectures, which results in large overhead from trying to interpret hardware instructions meant for one architecture as software instructions. The more authentic solution is to recreate the NES via hardware. Some advantages of genuine replication of the original architecture include zero performance overhead, as well as accurate execution of programs, including any bugs or exceptional cases in either program or hardware. The best way of recreating hardware designs quickly and flexibly is through a Field-Programmable Gate Array (FPGA); a chip of programmable hardware logic. In fact, this is not the first redesign of the NES using an FPGA.

There are a few products in the current market that allow the NES to be played. Nintendo officially sells the NES Classic: a smaller-sized version of the home console. This runs NES games through software emulation on an ARM processor, meaning there are inaccuracies with the emulation, and only works with games purchased in its separate online store. More market options include the Pocket and NT Mini from the company Analogue. Both are High-end hardware "emulators" built on FPGA's for not only the NES but other consoles as well. While both offer full recreation, and the Pocket is also portable, these systems are priced over \$300 and lock their FPGAs and hardware to prevent tampering. For more flexible hardware in such a way that it may require many external parts and multiple levels embedded hardware and circuit design knowledge. One example is the MiSTer FPGA. Our NES FPGA project will allow flexibility within the build; our solution aims to be portable, handheld, cost-effective, hardware unlocked, DIY-friendly, and modular.

## Approach

Since original NES consoles are not commercially sold anymore or are expensive to purchase secondhand, we want to develop a cheaper alternative that still maintains portability and simplicity. In addition, some current market alternatives use hardware locked FPGAs; we want our NES FPGA project to be "unlocked" to allow programmability to the BASYS-3 within in case the user wants to use the FPGA platform for another project.

In order to prototype our project, we start with the BASYS-3 and hardware language. Credit is given to Brian Bennett, who provided his recreation of the NES architecture written in Verilog, available to the public on GitHub. Input and output signals will be adjusted to match the pins of the BASYS-3. A VGA display, an NES controller, and an audio speaker will be required to playtest the emulated NES, along with two BASYS-3 PMOD expansions for audio amplification and SD card readding. The NES architecture can be stored in the BASYS-3 as its default program via USB Universal Asynchronous Receiver-Transmitter (UART) communication, which can also load the NES game ROMs. This will be integrated into the Verilog code to read game ROMs from an SD card through Serial Peripheral Interface (SPI).

Additional components, such as a small LCD screen and a battery power source, will be chosen to allow the device to have portable/handheld functionality. To minimize the dimensions of our device, we will construct our own breakout board that will contain the audio amplifier circuit, SD card reading circuit, button interface circuit, and power management circuit.

Time and budget constraints may arise during the prototyping phase. There are several alternatives that can be made:

• External display, controllers, and audio instead of embedded

- Not using the BASYS-3, instead simply using an FPGA soldered to the breakout board

- Using a different storage solution as opposed to an SD card i.e., memory bank

- Using a wired power connection as opposed to battery

Using external components will make the device lose its portability and handheld functionality. Next, switching out the BASYS-3 with a soldered FPGA to the breakout board will minimize the device's dimensions. Another alternative is using a memory bank in the BASYS-3 to store game ROMs, although this would disallow a user to "plug and play" their own game ROMS via SD card. The last alternative is to use a wired power connection and eliminate the use of a battery. Handheld functionality can be preserved but portability of the device will be lost. These alternatives will greatly shift the time and budget specifications of this project.

As mentioned before, Brian Bennett's FPGA project of the NES architecture on GitHub will be implemented into the BASYS-3. He reports that his project is missing mappers and the Delta Modulation Channel (DMC). He also provides a C++ windows application named NesDbg that will allow communication to the FPGA via USB UART. NesDbg can be used to runs tests and to load game ROMs.

Nesdev Wiki provides a plethora of information on programming topics for the NES. It will prove to be useful when we start to develop a game selection menu and to change memory map values accordingly to each game stored on the SD card.

# **Project requirements specification**

### **Mission Requirements**

- The device shall emulate the original NES by creating a breakout board for the BASYS-3 board.

- The device will provide a new platform for emulating NES.

### **Operational Requirements**

### **Input/Output Requirements**

- The device shall output audio to either speaker or headphones.

- The device shall accept user input through push buttons.

- The device shall display video output to an LCD.

- The device shall have indicator LEDs

### **External Interface Requirements**

- The device shall read/load games via SD card/Memory chip.

- The SD card/memory chip should be programmable via micro-USB.

### **Functional Requirements**

- The device will start on a main menu.

- The device shall allow the user to be able to select a game on the menu.

- The device shall allow the user to adjust audio volume level.

- The device will run games at the same clock speed as the original NES @1.79MHz.

The device shall be able to continuously play for 3.3 hours on a full charge.

## **Technology and System-Wide Requirements**

- The device should cost less than \$150

- The device shall use the BASYS-3 board.

- The device should use VGA as its display interface

- The device should be portable.

# System Design

**Functional Decomposition (Level-0)**

**Functional Decomposition (Level-1)**

Functional Decomposition (Level-2): Accept User Input

## **Functional Decomposition (Level-2): Load Program**

### Functional Decomposition (Level-2): Battery Management

**Functional Decomposition (Level-2): Run Program Instructions**

### Functional Decomposition (Level-2): Control Display

Functional Decomposition (Level-2): Control Audio

## **Physical Architecture**

## System Architecture

## **Preliminary Experimental Plan**

Problems may arise when testing the prototype. To validate the requirements of our project, several experiments can be conducted:

- Audio and video synchronization

- Button response time

- Battery lifetime on full charge

For the audio and video synchronization experiment, a general test at the human sense level can be performed. A high frame rate video (at least 60 fps) and audio recording of the VGA display may be used in video editing software to confirm that audio, such as sound effects from a game, are synchronized with the actions within the game.

A button response time experiment can be done in the same manner of the experiment above, with a high framerate video recording (at least 60 fps) of the VGA display and a button being pressed. An estimated response time may be measured based on the amount of video frames it takes for the VGA display to change.

Lastly, a battery life experiment will help ensure we reach our calculated 3.3 hours of battery life for the device. The battery will initially be fully charged, then the experiment can be divided into sub-experiments:

- Idle battery lifetime

- Playtime battery lifetime

All the above experiments will need to be reconducted on the finalized device in ECE 493.

## **Preliminary Project Plan**

In ECE 493, we will begin to develop our finalized device. Our project will consist of five main tasks:

- o Circuit design

- PCB design

- Enclosure design

- Game selection menu program

- RTL code for memory

Brooks will be responsible for circuit design, with the help of Anthony. Their objective will be to design the circuitry for the breakout board. With the help of computer SPICE software, simulations can be conducted.

Amilcar will be responsible for designing the PCB layout, with the help of Brooks. They will need to use the circuit designed by Brooks and Anthony to design a PCB for the breakout board. They will also be responsible for soldering required electronic components to the PCB.

Once the breakout board dimensions and externals are finalized, Anthony will have the responsibility of designing the 3D-printed enclosure with the help of Amilcar. They will then construct the device will all necessary large components such as the LCD screen, battery, and speaker.

While the tasks above are sequential, Josh and Sam will be helping one another on the software/RTL responsibilities. Josh's main responsibility will be to create code for RTL functionality for manipulating memory locations in the memory map on the NES architecture. Sam, in tandem, will be responsible for programming and designing a game selection menu on boot-up to work with the RTL design.

## **Potential Problems**

During or before ECE 493, we will need to learn skills for our corresponding responsibility. Most notably, CAD software for both 3D modeling the enclosure and for designing the PCB. Programming-wise, our knowledge of VHDL and assembly code may help facilitate learning Verilog and 6502 assembly with respect. Those programming skills will be required to implement the SD card to read and load game ROMs. Without that implementation, we will have to fall back to NesDbg to load the game ROMs.

There are known missing functionalities in Brian Bennett's NES architecture. One of the missing functionalities is support for mappers. Some NES games use mappers to expand the normal limitations of their circuitry and memory in the ROM. Games that utilize mappers may not work as intended when play tested on the recreated NES architecture. Another missing functionality is the Delta Modulation Channel (DMC). The DMC is utilized in some NES games to be able to play a "sampled" sound, such as a vocal phrase, or a real-world acoustic instrument. Playable games in the recreated NES architecture will simply not be able to output the audio from the DMC.

From our testing of Brian Bennett's NES architecture, we noticed that the VGA display contains a yellow tint filter. We also noticed that some character sprites, such as Mario in Super Mario Bros., contain slight visual errors. We hypothesize that the visual errors may be caused by the type of display we used during play testing.

# References

- Literature references

- o <u>https://github.com/brianbennett/fpga\_nes</u>

- o <a href="https://wiki.nesdev.org/w/index.php?title=Nesdev\_Wiki">https://wiki.nesdev.org/w/index.php?title=Nesdev\_Wiki</a>

- o https://www.retrorgb.com/how-a-nes-controller-works.html

- o https://taywee.github.io/NerdyNights/nerdynights/nesarchitecture.html

- o https://www.masswerk.at/6502/6502\_instruction\_set.html

- People contacted

- Professor Jens-Peter Kaps

# 10. Appendix B: Design Document (ECE-492) ECE-492

# **DESIGN DOCUMENT**

# NES Handheld Emulation Breakout Board for the BASYS-3

### Abstract

There are several methods to emulate the NES, including software or hardware emulation, with the latter being a more authentic emulation. We will emulate the NES on a BASYS-3 FPGA and we will minimize overall cost of components needed to create a portable/handheld device. Our FPGA NES emulation device will be comparable to existing devices in terms of price and capabilities. We will be using existing functionalities of power systems and of Pmod accessories for the BASYS-3 to create a singular breakout PCB to interface with the BASYS-3.

Team Members: Joshua Thomas Riggs, Brooks Aaron Corbett, Anthony Thinh Tang, Samuel Kifle Kebadu, Amilcar Alejandro Paniagua Date of Submission: 5/9/2022 Faculty Supervisor: Jens-Peter Kaps

# **TABLE OF CONTENTS**

| 1. Problem Statement                    |  |

|-----------------------------------------|--|

| 2. Project requirements specification   |  |

| 2.1 Mission Requirements                |  |

| 2.2 Operational Requirements            |  |

| Input/Output Requirements               |  |

| External Interface Requirements         |  |

| Functional Requirements                 |  |

| Technology and System-Wide Requirements |  |

| 3. System Design                        |  |

| 4. Background Knowledge                 |  |

| 4.1 VGA Protocol                        |  |

| 4.2 SPI Protocol                        |  |

| 4.3 6502 CPU arch                       |  |

| 4.4 Power/battery Management            |  |

| 4.5 Bennet Open-Source NES              |  |

| 5. Detailed Design                      |  |

| 5.1 Software                            |  |

| 5.2 Hardware Components                 |  |

| 6.1 List of components                  |  |

| 6.2 Current experimental setup          |  |

| Controller                              |  |

| Display                                 |  |

| Audio                                   |  |

| SD Card                                 |  |

| Battery                                 |  |

| 6.3 Prototyping History                 |  |

| 6.4 What we learned                     |  |

| 6.5 Current Roadblocks                  |  |

| 6.6 Predicted Roadblocks                |  |

| 6.7 Bonus Roadblocks                    |  |

| 6.8 Testing Plan                        |  |

| 6.9 List and Description of Tasks       |  |

| 7. Schedule and Milestones |  |

|----------------------------|--|

| 7.1 Next Semester Plans    |  |

| 7.2 Milestones             |  |

| 7.3 Gantt Chart            |  |

| 8. References              |  |

### **1. Problem Statement**

Within the past decade, older/retro games are becoming much more difficult to acquire. As such, many players in the gaming community turn to emulation to preserve their beloved games. Video game console emulation can vary in range of prices, with each method containing their advantages and disadvantages. We are motivated to seek a more cost-effective method for hardware emulating the NES in a portable package, meant to be hand-operated with a selfcontained power source. We are also motivated to bring a new option for NES emulation with the BASYS-3.

As of Q1 2022, original NES home consoles can only be obtained secondhand. The most convenient method to play an NES is emulation by software. However, software emulation runs on personal computers with general architectures, which results in large overhead from trying to interpret hardware instructions meant for one architecture as software instructions. The more authentic solution is to recreate the NES via hardware. Some advantages of genuine replication of the original architecture include zero performance overhead, as well as accurate execution of programs, including any bugs or exceptional cases in either program or hardware. The best way of recreating hardware designs quickly and flexibly is through a Field-Programmable Gate Array (FPGA), a chip of programmable hardware logic. In fact, this is not the first redesign of the NES using an FPGA [3].

There are a few products in the current market that allow the NES to be played. Nintendo officially sells the NES Classic: a smaller-sized version of the home console. This runs NES games through software emulation on an ARM processor, meaning there are inaccuracies with the emulation, and only works with games purchased in its separate online store. More market options include the Pocket and NT Mini from the company Analogue. Both are High-end

hardware "emulators" built on FPGA's for not only the NES but other consoles as well. While both offer full recreation, and the Pocket is also portable, these systems are priced over \$300 and lock their FPGAs and hardware to prevent tampering. For more flexible hardware implementations, there are DIY options. Some DIY projects, however, are complex in such a way that it may require many external parts and multiple levels embedded hardware and circuit design knowledge. One example is the MiSTer FPGA. Our NES FPGA project will allow flexibility within the build; our solution aims to be portable, handheld, cost-effective, hardware unlocked, DIY-friendly, and modular.

# 2. Project requirements specification

In our preliminary brainstorming we came up with a few requirements that our design requires. Mission Requirements are abstract and design independent and focus on how our design relates with external uses. Operation requirements specify what the input and outputs are, what the external interfaces are, any specific functional requirements and any technology requirements. These requirements were chosen with input from our stakeholder Dr. Kaps.

### **2.1 Mission Requirements**

- The device shall emulate the original NES by creating a breakout board for the BASYS-3 board.

- The device will provide a new platform for emulating NES.

### **2.2 Operational Requirements**

### **Input/Output Requirements**

- The device shall output audio to either speaker or headphones.

- The device shall accept user input through push buttons.

- The device shall display video output to an LCD.

- The device shall have indicator LEDs

### **External Interface Requirements**

- The device shall read/load games via SD card/Memory chip.

- The SD card/memory chip should be programmable via micro-USB.

### **Functional Requirements**

• The device will start on a main menu.

- The device shall allow the user to be able to select a game on the menu.

- The device shall allow the user to adjust audio volume level.

- The device will run games at the same clock speed as the original NES

@1.79MHz.

- The device shall be able to continuously play for 3.3 hours on a full charge.

### **Technology and System-Wide Requirements**