# $\frac{\text{IPSEC IMPLEMENTATION IN EMBEDDED SYSTEMS FOR}}{\text{PARTIAL RECONFIGURABLE PLATFORMS}}$

by

Ahmad Salman A Thesis Submitted to the Graduate Faculty of George Mason University In Partial fulfillment of The Requirements for the Degree of Master of Science Computer Engineering

Committee:

|       | Dr. Jens-Peter Kaps, Thesis Director                                               |

|-------|------------------------------------------------------------------------------------|

|       | Dr. Kris Gaj, Committee Member                                                     |

|       | Dr. Craig Lorie, Committee Member                                                  |

|       | Dr. Andre Manitius, Chairman, Department<br>of Electrical and Computer Engineering |

|       | Dr. Lloyd J. Griffiths, Dean, Volgenau<br>School of Engineering                    |

| Date: | Summer Semester 2011<br>George Mason University<br>Fairfax, VA                     |

IPsec Implementation in Embedded Systems for Partial Reconfigurable Platforms

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science at George Mason University

By

Ahmad Salman Bachelor of Engineering Arab Academy for Science and Technology, 2002

Director: Dr. Jens-Peter Kaps, Professor Department of Electrical and Computer Engineering

> Summer Semester 2011 George Mason University Fairfax, VA

Copyright © 2011 by Ahmad Salman All Rights Reserved

# Dedication

I dedicate this thesis to my parents, Ali Salman and Fatma Mahmoud, my sisters Mona, Hadeel and Inas, my brother Akram for believing in me and for their endless support.

# Acknowledgments

First I wish to thank my advisor Dr. Jens-Peter Kaps for his guidance, support and endless patience during the time it took me to finish the thesis work and for making all the resources and equipment I needed available. I'm really fortunate to have him as an advisor and teacher.

Secondly, I would like to thank Dr. Kris Gaj for his valuable input, guidance and remarks and and Dr. David Hwang for pointing me to the right direction and providing a starting point for the thesis as well as valuable resources. I'd also like to thank Dr. Craig Lorie for the time he provided, valuable comments and for understanding when I did not fulfill my duties as his TA on time during my thesis work.

Finally, a special thanks to my friend and colleague Marcin Rogawski for his help, support and providing valuable resources essential to finishing this thesis. I'd like to thank all my friends and colleagues in the Cryptographic Engineering Research Group (CERG) for their help and support.

# Table of Contents

|     |        | $\operatorname{Page}$                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|

| Lis | t of T | Tables                                                                                                                      |

| Lis | t of F | $ m in gures \ldots viii$ |

| Ab  | stract | ix                                                                                                                          |

| 1   | Intr   | oduction                                                                                                                    |

|     | 1.1    | Overview                                                                                                                    |

|     | 1.2    | Method                                                                                                                      |

|     | 1.3    | Thesis Outline    3                                                                                                         |

| 2   | Rela   | ated Work and Motivation                                                                                                    |

|     | 2.1    | Hardware Implementations and FPGA                                                                                           |

|     | 2.2    | IPsec                                                                                                                       |

|     | 2.3    | IP Cores                                                                                                                    |

| 3   | Bac    | kground                                                                                                                     |

|     | 3.1    | Overview                                                                                                                    |

|     | 3.2    | Boards                                                                                                                      |

|     |        | 3.2.1 XUP Virtex-II-Pro Development System                                                                                  |

|     |        | 3.2.2 ML403 Evaluation Platform                                                                                             |

|     | 3.3    | FPGA Architecture    13                                                                                                     |

|     |        | 3.3.1 XC2VP30 FPGA                                                                                                          |

|     |        | 3.3.2 XC4VFX12 FPGA                                                                                                         |

|     | 3.4    | Configuration                                                                                                               |

|     |        | 3.4.1 XUP Virtex-II-Pro Configuration                                                                                       |

|     |        | 3.4.2 ML403 Configuration                                                                                                   |

|     | 3.5    | Tools                                                                                                                       |

|     |        | 3.5.1 Xilinx Embedded Development Kit (EDK) 16                                                                              |

|     |        | 3.5.2 Xilinx Integrated Software Environment (ISE)                                                                          |

|     |        | 3.5.3 PlanAhead                                                                                                             |

|     | 3.6    | 9.5.5.5   FlamAnead   12     Partial Reconfiguration   19                                                                   |

|     | 0.0    |                                                                                                                             |

|     |        | 3.6.1 Introduction                                                                                                          |

|     |        | 3.6.2 Early Access Partial Reconfiguration                                                                                  |

|   |     | 3.6.3   | Internal Configuration Access Port | 22 |

|---|-----|---------|------------------------------------|----|

|   |     | 3.6.4   | Bus Macros                         | 24 |

| 4 | Imp | lementa | ation Methodology                  | 27 |

|   | 4.1 | Overvi  | iew                                | 27 |

|   | 4.2 | Design  | Description Overview               | 28 |

|   | 4.3 | Hardw   | vare Architecture                  | 30 |

|   |     | 4.3.1   | Processor Cores and Buses          | 30 |

|   |     | 4.3.2   | Software Architecture              | 40 |

|   |     | 4.3.3   | Hardware-Software Synchronization  | 43 |

| 5 | Exp | eriment | t Methodology                      | 48 |

|   | 5.1 | Overvi  | iew                                | 48 |

|   | 5.2 | Static  | Portion Of The System              | 48 |

|   | 5.3 | Dynan   | nic Portion Of The System          | 49 |

|   | 5.4 | Design  | a Synthesis and Top-Level creation | 50 |

|   | 5.5 | Design  | n Floorplanning and Implementation | 50 |

|   | 5.6 | Proble  | ems                                | 53 |

| 6 | Res | ults .  |                                    | 55 |

|   | 6.1 | Device  | e Utilization Summary              | 55 |

|   | 6.2 | Time 1  | Measurements                       | 58 |

| 7 | Con | clusion |                                    | 61 |

# List of Tables

| Table | P                                                                          | age |

|-------|----------------------------------------------------------------------------|-----|

| 2.1   | IPsec Supported Protocols and Algorithms                                   | 7   |

| 3.1   | XC4VFX12 Basic Features                                                    | 14  |

| 6.1   | Resources Summary for Implementations on ML403 Board                       | 55  |

| 6.2   | Resources Summary for PowerPC Implementations on Virtex-II-Pro $\ .\ .\ .$ | 57  |

| 6.3   | Resources Summary for Microblaze Implementations on Virtex-II-Pro $~$      | 58  |

| 6.4   | Average Reconfiguration Speed on Both Platforms For Two Different Designs  | 60  |

# List of Figures

| Figure |                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------|------|

| 1.1    | A High-Level Diagram of the Design                                                         | 3    |

| 2.1    | Authentication Header and Encapsulating Security Payload Formats                           | 6    |

| 3.1    | XUP Virtex II-Pro Board and Some Peripherals                                               | 10   |

| 3.2    | ML403 Board and Some Peripherals                                                           | 12   |

| 3.3    | ICAP Configuration Process                                                                 | 23   |

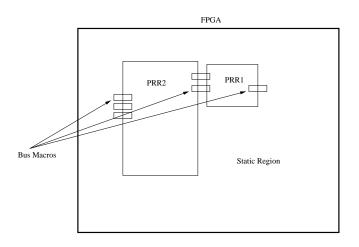

| 3.4    | Bus Macros Used to Lock Routing Between PRMs and BDM $\ .$                                 | 24   |

| 4.1    | Embedded System Processor and Peripherals                                                  | 29   |

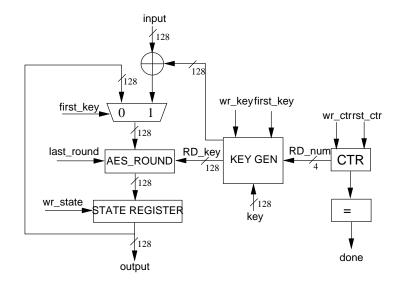

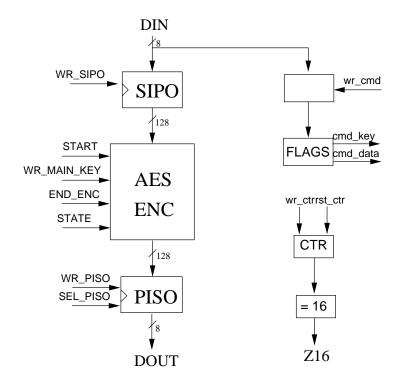

| 4.2    | AES Datapath                                                                               | 34   |

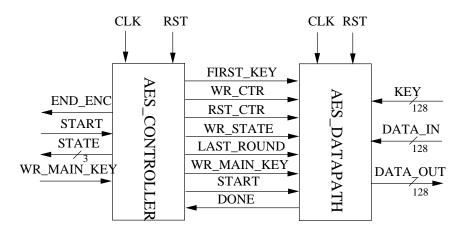

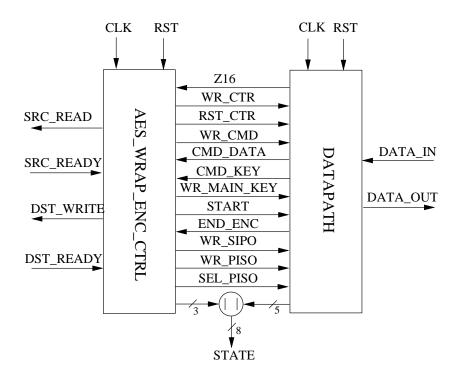

| 4.3    | Top-Level Diagram for AES Encryption Module                                                | 35   |

| 4.4    | Top-Level Diagram for AES Wrapper                                                          | 35   |

| 4.5    | AES Wrapper                                                                                | 36   |

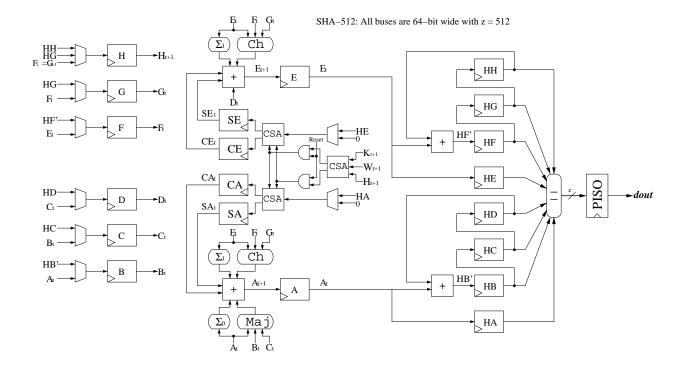

| 4.6    | SHA-256 Datapath                                                                           | 37   |

| 4.7    | SHA-256 Datapath                                                                           | 38   |

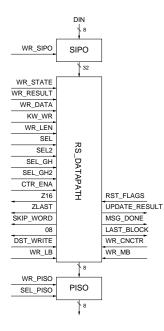

| 4.8    | SHA-256 Wrapper                                                                            | 38   |

| 4.9    | SHA-256 Command Flag                                                                       | 39   |

| 4.10   | Synchronization Circuit Between Hardware and Software                                      | 45   |

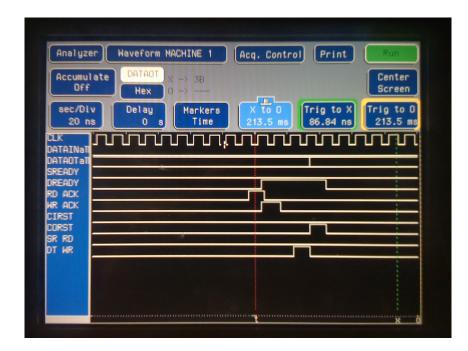

| 4.11   | Logic Analyzer Waveform Triggered at src_ready                                             | 46   |

| 4.12   | Logic Analyzer Waveform Triggered at dst_ready $\ldots \ldots \ldots \ldots \ldots \ldots$ | 47   |

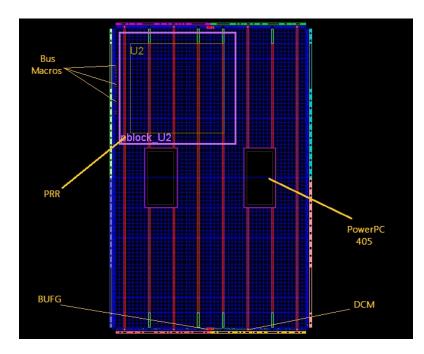

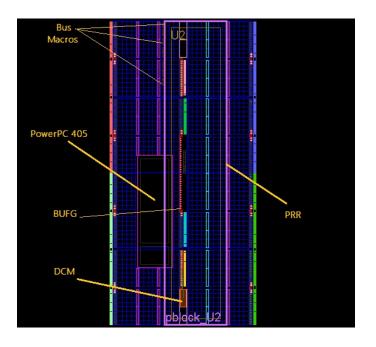

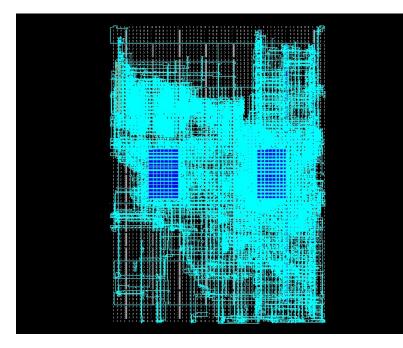

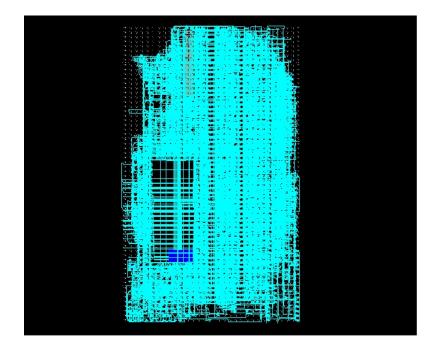

| 5.1    | Virtex-II-PRO FPGA After Floorplanning                                                     | 51   |

| 5.2    | Virtex-4 FPGA After Floorplanning                                                          | 51   |

| 5.3    | Virtex-II-PRO FPGA After Implementation                                                    | 52   |

| 5.4    | Virtex-4 FPGA After Implementation                                                         | 53   |

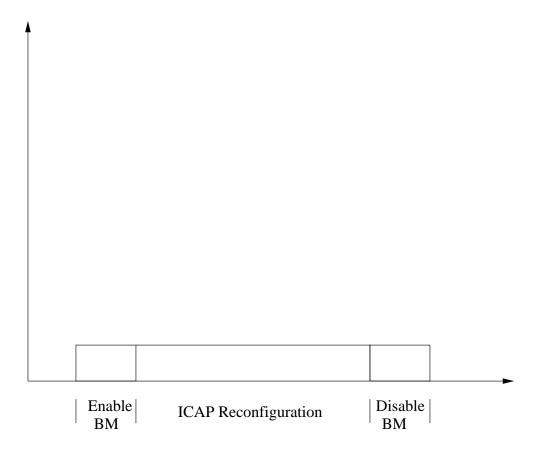

| 6.1    | Total Time Needed for Partial Reconfiguration                                              | 59   |

# Abstract

#### IPSEC IMPLEMENTATION IN EMBEDDED SYSTEMS FOR PARTIAL RECONFIGURABLE PLATFORMS

Ahmad Salman

George Mason University, 2011

Thesis Director: Dr. Jens-Peter Kaps

Internet Protocol Security (IPsec) provides essential security against attacks on data transmitted over the Internet through different security services provided by cryptographic algorithms like encryption modules and hash functions. Due to the importance of IPsec, it has been implemented in hardware and software with different designs and parameters to suit different platforms and provide better solutions. Among the popular implementations of IPsec in hardware are those that target FPGA platforms because of the flexibility they offer the designer, ease of programming and high speeds that cannot be achieved through software. Due to the fact that FPGAs are resource limited devices, even efficient implementations of IPsec with all the services it provides might not fit on low cost devices or low area devices that are meant for light weight implementations. A solution to this problem can be Partial Reconfiguration which allows some IPsec services to be available in the system and the remaining services can be recalled when needed by an application. Partial Reconfiguration is a configuration method for FPGAs that allows certain portions of the device to be reconfigured during run-time without affecting other portions in the system or their functionality. In this thesis we will investigate the effect of implementing IPsec services using Partial Reconfiguration in terms of speed, area and reconfiguration time.

For that, we built an embedded system controlled through an embedded processor to provide self reconfiguration of the system through a software application. We also implemented different versions of the embedded system using Microblaze and PowerPC embedded processors targeting two different platforms (Virtex-4 and Virtex-II-Pro) to perform thorough testing on the proposed design and analyze the results.

# Chapter 1: Introduction

# 1.1 Overview

In the last decade, the number of Internet users has increased by more than one billion users with a growth rate of 444.8% making the Internet users count to be a little over one fourth of the world population [1]. The use of the Internet by this huge number of users and groups vary from social interacting and networking to economical and on-line banking. This rapid increase in the number of users has opened the door to an increasing number of security threats and cyber attacks making the need for a secure system for Internet usage and global networks in general an essential demand. Internet Protocol Security (IPsec) is a security protocol that provides security against a number of cyber attacks including Eavesdropping, Hacking, Phishing and IP Spoofing [2] through a number of security services like confidentiality, data integrity and authentication. Due to the overwhelming amount of data transfered over global networks, software implementations of protocols like IPsec have become impractical as software implementations cannot handle this much data processing and computations within a reasonable response time [3].For this reason, such computations are performed in hardware.

Hardware implementations not only perform at significantly higher speeds compared to software, but they also provide better protection to schemes implemented on them against attacks that software implementations are vulnerable to like viruses. Field Programmable Gate Arrays (FPGA) have become more popular as platforms for hardware implementations due to the fact that they provide flexibility, fast production time-line and are cost effective. For these reasons, they have been used as hardware accelerators in routers and other network devices to implement protocols like IPsec and Secure Socket Layer (SSL) [4]. One of the major advantages FPGA platforms provide is reconfigurability which facilitates system updates and upgrades. A relatively new feature of FPGA platforms, is Partial Reconfiguration in which part of the chip is reconfigured while the remaining portion is operational giving designers more options to efficiently use available resources.

Design implementations that take advantage of partial reconfiguration have shown promising results in terms of area saving and reduction in power consumption [5]. Although there are a number of researches on IPsec implementations on FPGA platforms, non of them take advantage of partial reconfiguration for efficient resource usage which can be beneficial to light-weight implementations targeting resource limited platforms. We would like to introduce a System-on-Chip (SoC) embedded system capable of performing IPsec protocol services in hardware having only the modules that are in use at any given time residing on the chip using partial reconfiguration. We will examine how useful such systems can be in terms of saving area and the amount of time needed to partially reconfigure the system. In the next sections we will present the method we used to achieve our goal and the outline of the thesis.

# 1.2 Method

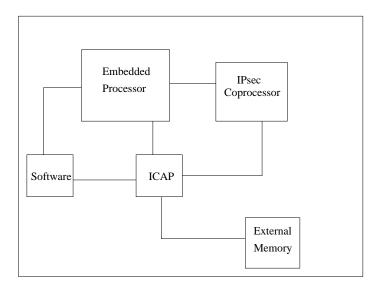

The embedded system we are proposing is composed of an embedded microprocessor, hardware modules to perform IPsec operations in hardware, system supporting peripherals and software support to create an Application Programming Interface (API) for different on-chip peripherals. Figure 1.1 shows a high level diagram with major components of the design. The embedded processor used in the system is either a Microblaze or PowerPC which will be discussed later. This embedded processor controls partial reconfiguration of the system through a module called the Internal Control Access Port (ICAP) which allows the system to be self-reconfigurable without user involvement.

Partial reconfiguration of the system takes place between two Intellectual Property (IP) Cores one is to perform encryption operations required by IPsec to provide confidentiality

Figure 1.1: A High-Level Diagram of the Design.

and the other core is to perform hash calculations to provide authentication and data integrity. Depending on the application being processed by IPsec and the services required, the microprocessor performs partial reconfiguration to load the suitable core for the requested operation.

Xilinx ISE,EDK and PlanAhead tools were used through out different design and implementation phases of the embedded system.The target devices for the created designs are Virtex-II-Pro and Virtex-4 devices on XUP Virtex-II-Pro and ML403 boards, respectively.

# **1.3** Thesis Outline

The thesis will be organized as follows. Chapter 2 presents the related work and motivation. In chapter 3 an overview of the target platforms, the FPGA devices on them, Xilinx tools used and partial reconfiguration technique will be presented. Chapter 4 explains the hardware architecture with different modules in the system as well as the software. In chapter 5 we present the implementation methodology and different design phases. In Chapter 6 the results are presented and discussed. Finally, chapter 7 provides the thesis conclusion.

# Chapter 2: Related Work and Motivation

### 2.1 Hardware Implementations and FPGA

In the past few years, hardware implementations of some network protocols, especially those related to providing network security services like IPsec and Secure Socket Layer (SSL), have increased due to the fact that data transfer rates have increased to the level of Tera-bits per second which demands shorter response time and higher processing speed for data which cannot be achieved through traditional software implementations that fails to handle high data throughput rates. One of the known platforms for hardware implementations of network security protocols is Network Security Processors (NSP) which can perform various cryptographic operations specified by these network security protocols [6]. But like Application Specific Integrated Circuit (ASIC) solutions, NSPs do not offer much flexibility as they are not re-programmable platforms[7]. Field Programmable Gate Arrays (FPGA) offer a System-on-Chip (SoC) solution with more flexibility for hardware implementations. The main advantages that FPGA implementations have over ASICs are

- With FPGAs, it is possible to reconfigure the chip for different encryption standards and hash algorithms to provide the services offered by different security services.

- Bug fixes in an existing implementation or upgrades to new standard can be easily achieved with little to no cost.

- FPGAs offer lower cost for small volumes, shorter development times and faster time to market over ASIC technology [8].

Although the throughput achieved by FPGA devices is less than that of ASICs, implementations on FPGA platforms have achieved throughput up to Giga-bits/second [6] making it suitable for network security protocols implementations and as hardware accelerators for Virtual Private Networks (VPN).

In addition to the previous benefits, FPGA devices can also be partially reconfigurable allowing reconfiguration of part of the chip without affecting the functionality of other modules running on it. This technique makes it possible to implement the same design on FPGAs with fewer resources or add more modules to a design on an existing FPGA without increasing the area.

Several implementations for network security services and hardware accelerators for IPsec in specific have targeted FPGA platforms [9] [10] [11] some of which only implemented only some modules for Authentication and not all services [12] [13] but non of which took advantage of partial reconfiguration although it would add to the system flexibility specially in light weight implementations where resources are very limited and area is a key factor. A partially reconfigurable system is presented in [14] where security is provided to bitstreams used to partially reconfigure specific regions in a reconfigurable system through IPsec but the protocol itself was implemented in software. For this reason, we wanted to implement a hardware accelerator for IPsec with the option of not having all encryption and hash functions residing on the chip thus taking advantage of partial reconfiguration. Not only that this will allow the use of less resources available on an FPGA, it will also make implementing all the supported cryptographic algorithms possible on small FPGA devices giving users the freedom to choose between all supported algorithms by a protocol and also the possibility of adding new algorithms in the future if they become part of the protocol standard.

#### 2.2 IPsec

IPsec is a security protocol that provides security for data being transmitted over unsecured networks like the Internet [15]. operating in the Internet layer of the TCP/IP model, IPsec provides security to IP packets being transfered between hosts and gateways in IPV4 and IPV6 through different cryptographic functions.

IPsec provides a number of security services for data protection that can be summarized

in the following points as defined in [16]

- *Confidentiality:* Which is keeping information secret from all but those who are authorized to see it.

- *Authentication:* Can be corroboration of the identity of an entity or corroborating the source of information.

- *Data integrity:* Ensuring information has not been altered by unauthorized or unknown means.

In addition to the previous services, IPsec also provides key management through Internet Key Exchange (IKE) mechanism which allows the exchange of secret keys over unsecured networks like the Internet.

These services are provided by IPsec through two main protocols Authentication Headers (AH) and Encapsulating Security Payload (ESP). The IP AH is used to provide connectionless integrity and data origin authentication for IP datagrams (i.e. integrity) and to provide protection against replays [17].For this AH uses Hash Message Authentication Code (HMAC) with a hash function to calculate Integrity Check Value (ICV). The AH format is illustrated in Figure 2.1 a

| Original<br>IP Header | AH<br>Header | TCP/ UDP | Data |

|-----------------------|--------------|----------|------|

|-----------------------|--------------|----------|------|

### a) AH Authentication

| Original<br>IP Header | ESP<br>Header | TCP/ UDP | Data | ESP<br>Trailer |

|-----------------------|---------------|----------|------|----------------|

|-----------------------|---------------|----------|------|----------------|

#### b) ESP Encryption

Figure 2.1: Authentication Header and Encapsulating Security Payload Formats

The IP ESP is designed to provide a mix of security services in IPv4 and IPv6. It can be used to provide confidentiality, data origin authentication, connectionless integrity, an anti-replay service [18]. For confidentiality, EPS uses encryption ciphers like Data Encryption Standard (DES) or Advanced Encryption Standard (AES). It can also be used in combination with AH to provide Confidentiality and Authentication. Figure **??** b shows the EPS format.

In addition to AH and EPS, IPsec uses Security Association (AS) concept to provide necessary parameters needed by AH and EPS like encryption keys. Also Internet Security Association and Key Management Protocol (ISAKMP) which is used for key exchange and to authenticate keys. Table 2.1 summarizes the protocols supported by IPsec, their functionality and the algorithms currently supported.

| Protocol                                         | Security Service Provided            | Supported Algorithm          | Modes of Operation |

|--------------------------------------------------|--------------------------------------|------------------------------|--------------------|

| ESP                                              | Provides Confidentiality through     | AES and TripleDES            | CBC and CTR        |

| Encapsulating Security Payload                   | data encryption                      |                              |                    |

| AH                                               | provide connectionless integrity and | HMAC-SHA1-96, AES-MAC-96,    | XCBC               |

| Authentication Header data origin authentication |                                      | HMAC-MD5-96 and HMAC-SHA-256 |                    |

| IKE                                              | Negotiates connection parameters,    | Deffie-Hellman and RSA       |                    |

| Internet Key Exchange                            | including keys, for the other two    |                              |                    |

Table 2.1: IPsec Supported Protocols and Algorithms

In some contexts, the term IPsec includes all three of the above but in other contexts it refers only to AH and ESP [19]. Sometimes not all three are included because of limitations in resources available on an FPGA platform which can be solved by using partial reconfiguration that allows same resources to be used with different modules giving the opportunity to add more algorithms to the protocol and the freedom to choose between the available ones.

# 2.3 IP Cores

Intellectual Property Core (IP Core) is a block unit composed of combinational and sequential logic to be used as a building block for larger block units or used in different designs without the need of rebuilding it. Usually, IP Cores are the intellectual property of of one party which issues licenses for this IP to be used by other parties or it can be solely used by this party only. IP cores are widely used in designing for FPGA platforms for various interfaces and embedded modules.

IP Cores comes in the following two different types

- *Hard Core:* Where the IP is hard-wired to the FPGA or integrated on-chip as a component. The benefit of hard cores is that they add to the chip performance in terms of area and time but the problem is that they are very vendor or foundry specific and not portable to different platforms.

- Soft Core: The soft IP cores are offered as synthesizable Register Transfer Level (RTL) in the form of hardware description languages like VHDL and Verilog which can be modified by the designer or they can be offered as netlists to prevent modification if the vendor chooses so. The benefit of soft IP cores is that if the vendor allows it, they can be adapted by different platforms like in case of open-source cores.

Lots of Vendors offer IP cores either through their Computer Aided Design (CAD) tools if the IP Core has copy right protection and they are specific to the vendor's hardware, or through open-source hardware language codes that can be adapted by any platform.

# Chapter 3: Background

# 3.1 Overview

Xilinx is a known supplier for digital Programmable Logic Devices (PLD) which includes Complex Programmable Logic Devices (CPLD) and Field Programmable Gate Arrays (FPGA). One of the high end FPGA products by Xilinx is the Virtex family series. Since the release of the original family in 1998, Virtex has delivered high-performance logic solutions offering more Block rams, Logic Cells, Input/Output (I/O) availability and Look Up Tables (LUT) than any other FPGA family series offered by Xilinx [20]. For the purpose of this research we will focus on two specific Virtex families, Virtex II-Pro and Virtex 4 and the development boards they are embedded on.

## 3.2 Boards

Xilinx provides hardware development boards with FPGA's of different families installed on-board. The boards provide basic and supplementary interfaces and IP cores to create a hardware environment which facilitates the designer's job in implementing a design. For this project, we needed a relatively high density platform that supports partial reconfiguration, as it is the basic idea of the project, for this reason we chose XUP Virtex-II-Pro Development System and ML403 Evaluation board as the platform for the research. In this section, we will be discussing both boards and the peripherals integrated on them.

#### 3.2.1 XUP Virtex-II-Pro Development System

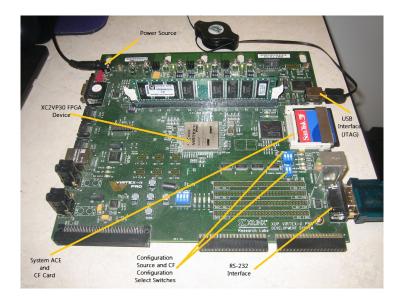

The XUP Virtex-II-Pro Development System is equipped with XC2VP30 FPGA device that features hight density 13,969 slices (30,816 logic cells), 428 Kb Distributed RAM and 2,448 Kb Block RAMs which allows flexibility of device configuration as well as embedded microprocessor controlled designs using the two PowerPC 405 embedded core blocks [21]. The XUP Virtex II-Pro board also features a number of peripherals as shown in Figure 3.1 , some of which are of importance to us which we can summarize in the following points

Figure 3.1: XUP Virtex II-Pro Board and Some Peripherals

- 1. Multi-Gigabit Transceivers: with eight rocket I/O Multi- Gigabit Transceivers (MGTs), the Virtex II-Pro provides high performance and fast communication between the board modules. Four of the available MGTs are available for user utilization though the board connectors and the other four are connected to the Serial Advanced Technology Attachment (SATA) interface. Using MGTs, the XC2VP30 FPGA can achieve a baud rate up to 3.21 Gb/s [22].

- 2. System Advanced Configuration Environment Controller: The System Advanced Configuration Environment (System ACE) controller provides multiple ways to configure the XUP Virtex II-Pro board. It controls the chain between the FPGA

and a number of configuration resources available to choose from. Through the System ACE controller, the FPGA on board can be configured using Joint Test Action Group (JTAG) port using Universal Serial Bus (USB) cable, Compact Flash Port using a Compact Flash (CF) card or it can be configured using the Microprocessor (MPU) port which is connected directly to the FPGA.

3. Serial Ports: Two PS/2 ports and one RS-232 port sums up the serial ports on XUP Virtex II-Pro board. The PS/2 interfaces are used for keyboard and mouse connections for user interaction. The RS-232 serial port interface is configured as a Data Communications Equipment (DCE) to allow communication with a terminal through a COM port of a host computer using a 9-pin serial connector.

#### 3.2.2 ML403 Evaluation Platform

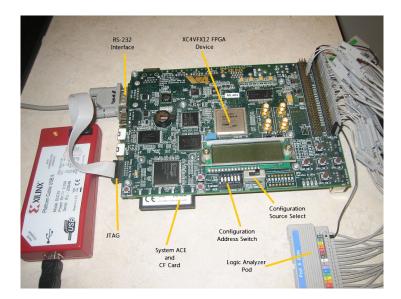

With a powerful XC4VFX12 Virtex 4 FPGA [23] installed on it, The ML403 Evaluation Platform provides enhanced high performance and low power programmable logic design capabilities which makes it an Application Specific Integrated Circuits (ASIC) alternative with the advantage of low cost and reconfiguration ability. The following illustrates some of the ML403 Evaluation Platform features as shown in Figure 3.2

Figure 3.2: ML304 Board and Some Peripherals

- 1. **DDR SDRAM:** The ML403 Evaluation Platform has 64MB DDR SDRAM installed on board divided into two 16-bit wide chips with 32-bit data bus which provides high data rate up to 266 MHz [24]. The DDR SDRAM chip is upgradeable to 256MB and can also be expanded through the on board slot which supports 1GB of external DDR RAM to be installed.

- 2. System ACE and Compact Flash Connector: Although the The ML403 Evaluation Platform can be configured through a Parallel IV JTAG cable, the System ACE allows the use of Type-I or Type-II compact flash cards to configure the FPGA through the system ACE. Using the address switch, the System ACE allows the user to choose between eight different configuration files on a single CF card.

- 3. Serial Ports: Like the XUP Virtex II-Pro board, the ML403 Evaluation Platform has two PS/2 interfaces for Keyboard and Mouse connections as well as a single RS-232 serial interface in which only Tx and Rx pins are connected to the FPGA and the rest of the 9-pins are not used. The RS-232 is optimized to perform on high 115200 baudrate to provide high speed communication with host devices.

# 3.3 FPGA Architecture

The XC2VP30 and the XC4VFX12 are the two FPGA chips installed on the XUP Virtex II-Pro and ML403 boards respectively as mentioned in the previous section. In this section we will discuss the architecture of each of these two FPGA chips and focus on the advantages that each can provide.

#### 3.3.1 XC2VP30 FPGA

The XC2VP30 is packaged in FF896 BGA package which provides a high capacity of logic units allowing large area designs to be easily configured on the device [22]. The basic features of the FPGA are illustrated in the following points.

- RocketIO MGT cores are parallel-to-serial and serial-to-parallel transceivers used to provide high bandwidth interconnection between buses and inter-system modules. RocketIO allows a data rate up to 3.125GB/s to be achieved.

- 2. Configurable Logic Blocks (CLB) contains the basic combinational and sequential logic units used for implementing designs. XC2VP30 has 3,424 CLBs each has four slices giving it a total of 13,696 slices making it easy to fit large area designs with more place and route options. There are two types of CLBs (F and G) which can be configured as 4 input Look-Up Tables (LUTs) or 16 bit shift registers.

- 3. Block RAM memory is cascadable memory which facilitates the implementation of large embedded storage blocks on the chip with the ability to "read-during-write" mode. XC2VP30 offers 2,448 Kb of block RAMs which can be configured in singleport or dual-port mode with a variety of depth and width settings.

- 4. Multiplier blocks which are used to perform read, multiplication and accumulation operations with the available 136 multiplier blocks available. The multiplier blocks can also be used to implement Digital Signal Processing (DSP) structures.

| Feature         | Available Resources |

|-----------------|---------------------|

| CLBs            | 1,368               |

| Slices          | $5,\!472$           |

| Logic Units     | 12,312              |

| Distributed RAM | 86                  |

| Block RAMs      | 648 Kb              |

| DCMs            | 4                   |

| PowerPC Cores   | 1                   |

| DSP Slices      | 32                  |

Table 3.1: XC4VFX12 Basic Features

- 5. Digital Clock Managers (DCMs), eight available, which provides various functions like implementing a clock Delay Locked Loop (DLL) that can synchronize different input clocks to the same design. DCMs can also be used to implement Digital Frequency Synthesizer (DFS) which provides a multiple or division of input clock or they can also be used to implement a Digital Phase Shifter (DPS).

- 6. PowerPC 405 (PPC405) Processor block is the on-chip embedded core for embedded systems implementations. There are two available PPC405 blocks for dual-core implementations. The structure of PPC405 will be discussed in details in the next chapter.

### 3.3.2 XC4VFX12 FPGA

The XC4VFX12 is produced on CMOS 90nm copper process technology based on enhanced basic blocks from Virtex- II and Virtex-II Pro FPGAs making it up to 40% faster than previous Virtex generations [25]. Packaged in FF668 package, XC4VFX12 provides 320 I/Os giving designers freedom in design interface choices. The basic features of the FPGA are shown in Table 3.1.

Since Virtex-4 is based on Virtex-II and Virtex-II Pro, the XC4VFX12 FPGA has the same features as XC2VP30 with some differences in numbers and sizes of the available resources. The basic features are shown in the following table DSP slices can perform all operations performed by the multiplier blocks found in Virtex-II Pro FPGAs with up to 100 % in speed improvement over previous generation devices. They also provide more efficient implementation of DSP structures using dedicated DSP units with the option of using pipeline stages.

# 3.4 Configuration

Both XUP Virtex II-Pro and ML403 platforms provide several configuration options to the FPGAs installed on them using on-board jumpers and switch settings. We will discuss the settings for each board and configuration options below.

#### 3.4.1 XUP Virtex-II-Pro Configuration

The XUP Virtex II-Pro board can be configured internally using the on-board Platform Flash configuration PROM or externally using other JTAG configuration options. There are two settings for the PROM configuration control switch, which if set to on, allows the PROM to configure the FPGA directly with a pre-configured Xilinx test configuration and if set to off, the PROM programs the FPGA using user configuration which must be already programmed on the on-board Platform Flash configuration PROM using one of the external configuration options.

Configuring the FPGA externally is done through JTAG which supports three different methods

- 1. The Compact Flash (CF) card which can hold up to eight configuration files and using configuration DIP switches, the desired configuration file can be selected.

- 2. The Parallel Cable IV (PC4) is connected on board through the JTAG configuration port which can also be used for hardware debugging.

- 3. The USB to PC connection which allows bitstreams created by programming tools to be downloaded to the FPGA through embedded Platform cable USB interface.

#### 3.4.2 ML403 Configuration

Through the configuration source selector, users can choose between four different methods to configure the FPGA installed on the ML403 board. Like the Virtex-II Pro Platform, the ML403 board supports the CF card and Parallel Cable IV JTAG configuration methods controlled by the system ACE controller. The other two configuration methods are

- 1. The Platform Flash memory which can hold up to four configuration images selectable through the configuration address DIP switches. The Platform Flash memory can configure the FPGA with bitstreams in four different modes selectable through iMPACT programming tools.

- 2. The Linear Flash which is capable of holding up to eight configuration images that can be used to configure the FPGA if read by the on-board CPLD in the JTAG chain.

### 3.5 Tools

Most of the steps in FPGA implementation are done by using CAD tools. From designing the system using HDL to adding peripherals to running place and route for a desired device, all is performed by different designing tools. In this section we will be discussing different tools that were used during the research and their role in building the system.

#### 3.5.1 Xilinx Embedded Development Kit (EDK)

Xilinx Embedded Development Kit (EDK) is a design suite of hardware tools, software tools and Intellectual Property (IP) which work together to develop a complete embedded processor SoC to be implemented on programmable platforms and devices [26]. EDK facilitates, for the designer, the development of the hardware part along with the software portion of an embedded system through tools offered by the kit which we will illustrate in the following points.

1. Xilinx Platform Studio (XPS): Using either the command line or the GUI, XPS

is used to design the hardware portion of the embedded processor system. The GUI has a wizard called the Base System Builder (BSB) which allows users to choose the processor they want to use in the system, clock and reference speeds, memory and IP cores and it creates the Microprocessor Hardware System (MHS) file according to the chosen options. The MHS file contains the hardware properties of the system and it can be edited by the user to change peripherals options and memory allocations. XPS also allows users to choose the bus type and connection interface between the embedded processor and the system peripherals along with the ability of connecting different bus types through bus bridges. Each peripheral in the system has an allocated address space depending on its size. XPS can generate the beginning and the ending of this address space automatically or the user can specify their own address space or modify the generated one by modifying the MHS file.

2. Software Development Kit (SDK): Although XPS can be used to implement the software portion of the embedded processor system, EDK has a supplementary tool dedicated for that purpose known as the SDK. Based on the open source tool Eclipse, SDK provides a software development environment for the embedded system by compiling the Microprocessor Software System (MSS) file, which contains the software description of the system peripherals, along with a C/C++ source code and peripherals drivers to create an Executable and Linker Format (ELF) file which when combined with the hardware implementation files, they create the bitstream configuration used to configure the board with the embedded system configurations. SDK is also used for debugging the software portion of the system by communicating with the system processor through the Xilinx Microprocessor Debugger (XMD) interface.

#### 3.5.2 Xilinx Integrated Software Environment (ISE)

Xilinx Integrated Software Environment (ISE) is a collection of software utilities that facilitates FPGA design and implementation procedure all integrated in a single tool. ISE provides utilities for design entry, design verification, synthesis, timing analysis, on-chip place and route and programming target devices. Design entry in ISE can be done through an schematic editor or by writing Hardware Description Language (HDL) codes using Verilog or VHDL programming languages. Design verification is provided by running behavioral or function simulation through supported simulation tools.ISE has the option to optimize designs for area or speed depending on user choices when synthesizing a design and the target device. Although an embedded processor system can be created and implemented using only EDK, it still needs to call the synthesis libraries from ISE to synthesis and implement the design or to simulate it for verification.

#### 3.5.3 PlanAhead

PlanAhead is a Xilinx software tool used for design analysis and floorplanning. The role of PlanAhead in Xilinx FPGA design flow, comes after synthesis and netlists are generated [27]. If a design synthesis and implementation processes were completed in ISE, PlanAhead can be used to analyze the implementation results, performs time analyses and checks for better implementation strategy for the target device if available. Like the FPGA Editor tool, PlanAhead can be used for floorplanning which allows designers to manually place design components after synthesis then the tool can check afterwards for timing constrains and design rules violations. It also issues warnings when not using the best available resources in the target device as well as recommending the best available resources and strategy to implement the design. PlanAhead can perform Translate and Place-and-Route of a synthesized design to generate a configuration file. It can also be used to perform floorplanning for partially reconfigurable designs where static and dynamic regions of the design can be defined and DCM and other resources are implemented accordingly on the target device [28].

# 3.6 Partial Reconfiguration

#### 3.6.1 Introduction

FPGA is a reconfigurable platform where it can be configured and reconfigured by designers through an implementation process from writing the design specifications using HDL codes to generating and downloading the bitstream that is used to configure the FPGA. Each time an FPGA device is being configured, it requires erasing the previous configuration or overwriting it completely with the new configuration bitstream and the whole device is on halt until the new configuration is completely downloaded. As mentioned before, Partial Reconfiguration (PR) is a method of reconfiguring part of the FPGA device while the rest of the device is up and running without getting affected by the downloaded partial bitstream configuration. The main advantages of using partial reconfiguration is that it allows for more logic to fit into an existing device by making the modules in the design partially reconfigurable and swapping between them as needed, and having the flexibility in adding more options to the design modules without the need to re-run Place-and-Route.

Partial reconfiguration method is independent of its implementation method meaning that although the idea of creating a partially reconfigurable designs is one, different companies and PLD manufacturers like Xilinx, Altera and Actel have their own tools and implementation methods to create such designs that differ from one another. Xilinx initially introduced two methods for partial reconfiguration on their devices known as Difference-Base Partial Reconfiguration and Module-Base Partial Reconfiguration [29]. The Difference-Base is a simple method used for small designs where the partial bitstream includes only information about differences between currently running design and the modifications that were made hence the name. Modifying Difference-Base designs is mainly done by changing the LUT equations. Module-Base partial reconfiguration divides the design into base or static region and partial reconfigurable region, the static region holds the part of the design that will not be replaced at anytime partial reconfiguration of the device takes place. The partial reconfigurable region is composed of one or more partial reconfigurable modules in which the portion of the design which will be dynamically partially reconfigured resides. Both methods are almost neither used by designers nor supported by Xilinx, instead Xilinx introduced Early Access Partial Reconfiguration method to replace both methods with added benefits and simplicity to partial reconfiguration process flow.

#### 3.6.2 Early Access Partial Reconfiguration

Early Access Partial Reconfiguration (EA PR) method is based on Module-Base Partial Reconfiguration in the sense that the design is divided into Base Region (BR) which is the static part of the design and Partial Reconfigurable Region (PRR) which is the dynamic part of the system composed of Partial Reconfigurable Modules (PRM) that can be swapped on the fly while the static part of the chip is operational. It is also based on Difference-Base Partial Reconfiguration in the sense that the partial bitstream modifies the configuration memory which includes modifying LUT equations as well as other aspects of user design. EA PR has seven steps to complete the design flow which we will illustrate in the following points

1. HDL Design Description and Synthesis: A Partially Reconfigurable design must first be described using either VHDL or Verilog languages and the design should be in a specific hierarchical manner which includes all static designs, known as the Base Design Modules (BDM), all Partially reconfigurable designs, known as Partial Reconfigurable Modules (PRM), and a system design which is the top-level module. The system design contains I/O of the entire design, global clock, DCMs, BUFGs and Bus Macro instantiations. Also all the BDMs and PRMs in the design are instantiated in the top level as black-box instantiations. BDMs represents the static portion of the system and it cannot contain any clock primitives and also I/O buffers should be disabled in the synthesis tools. Like BDMs, PRM cannot have BUFGs or DCMs or any other clock primitive instantiations and Each PRR should have at least one and usually multiple PRMs associated with that particular PRR and they should all have the same interface description and port definition. After the design description

is fulfilled, each of the modules is synthesized separately and the output is used in the implementation process.

- 2. Set Design Constraints: After the previously mentioned design description and synthesis is done, after synthesis (.ngc) files are generated which can be used to start the place-and-route process [30]. In addition to timing constraints that any design flow should follow, PR designs should follow additional area specific constraints known as Area Group (AG), Area Group Range (AR range), Mode and Location (LOC)constraints. AG constraints groups the BR logic and each PRR logic in the system separately to prevent them from merging during implementation. AG range constraints defines the shape and the area for each PRR in the design where the logic associated with that specific PRR and its PRMs are placed. The PRR defined by AG range has a rectangular shape and must include all the BRAMs that fall within the defined area. The mode constraint prevents NGDBUILD from failing with unexpanded block errors during base and PR module implementation. LOC constrains defines the global system logic (DCM, BUFG ... etc.) and bus macros placements. All these constraints can be defined manually by the user or by using PlanAhead to perform design floorplanning.

- 3. Implement the Non-PR Design: Although it is not required, it is recommended that a design should be synthesized, placed-and-routed and implemented as a non-PR design before implementing it with PR flow. The purpose of this is to make sure that the design is bug free and if not, it will simplify the design debugging and aids in determining the best AG constraints and bus macros placement.

- 4. **Timing/Placement Analysis:** After implementing the non-PR design, analyzing timing and placement of the logic is a very important step as it would reveal whether the PR region fulfills different constraints requirements and if the bus macros are placed correctly and do not violate any required conditions.

- 5. Implement the Base Design: If timing and placement analysis is successful, implementing the base design takes place. For successful implementation of the base design, after synthesis (.nmc) files for the bus macros instantiated in the design top level should be placed in the same folder as the base design. After implementation, the usual after place-and-route(.ncd) file is generated for the base design as well as *static.used* file which contains routing information of the static portion of the system to avoid using the same routs by the PRMs.

- 6. Implement PR Modules: Each PRM in the design should be implemented separately in its own folder and the generated static.used file from implementing the base design should be copied from the base folder to all other PRMs being implemented so that the routes used by the base design can be excluded from route choices when implementing PRMs. Also like base designs, PRMs require after synthesis (.nmc) files for bus macros to be included in each PRM folder, otherwise the NGDBuild step will fail.

- 7. Merge: The final step in EA PR flow is the merge step in which the base design and PRMs are being merged together to create a complete design and partial bitstreams. The completed design chooses the base design along with one of the PRMs to make the initial configuration bitstream file for the system and partial bitstreams are created for each PRM to be used during partial reconfiguration of the system.

All the previously mentioned steps can be done manually by the user by editing constraint files in ISE or by using PlanAhead which can simplify some of the steps by checking for violations in the constraints automatically and pointing them out to be fixed.

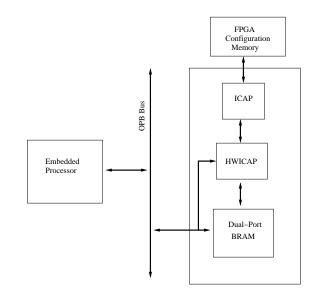

#### 3.6.3 Internal Configuration Access Port

We have already discussed some of the methods that can be used to configure the FPGA which require an external source (Like PC or CF card) to load configuration bitstreams. The Internal Configuration Access Port (ICAP) gives the user design the ability to write the configuration memory during run-time. Initially, The FPGA has to be externally configured with a complete design then ICAP can be used to reconfigure some portions of the FPGA. In embedded systems, the designer writes software programs which compiles to the microprocessor op-code instructions, these software instructions enables the microprocessor to read and write the configuration memory through ICAP. Modifying a design using ICAP is done with a technique known as read-modify-write mechanism where the portion of the system that needs to be modified is read in frames, one at a time, and stored in a BRAM. After all the frames have been read and stored in the BRAM, necessary modifications take place and the modified frames gets written back through ICAP same way they were read (i.e. one frame at a time) as shown in Figure 3.3.

Figure 3.3: ICAP Configuration Process

In Early Access Partial Reconfiguration, ICAP is used in the same way as described except that the modifications that needs to be done are in the form of partial bitsreams that resides in an external memory source (i.e. CF Card) but the difference between loading the data into configuration memory from an external source through ICAP and through any other configuration source (i.e. JTAG) is that ICAP only affects the portion of the design that it being modified or swapped through partial reconfiguration without interrupting the remaining of the design while other configuration sources affect the whole chip and reconfigures the design completely.

#### 3.6.4 Bus Macros

Because it is forbidden ,in partial reconfiguration, for static regions and partially reconfigurable regions to overlap and the routes used by the BDM cannot be used by PRMs, Early Access Partial Reconfiguration provides a component that allows communication between BDM and PRMs known as Bus Macros (BM) [30].Bus macros provide a mean of locking the routing between PRMs and the BDM, making PRMs pin compatible with the base design as shown in Figure 3.4. With the exception of global clock signals, all other signals including reset signals must pass through BMs when communications between BDMs and PRMs occur.

Figure 3.4: Bus Macros Used to Lock Routing Between PRMs and BDM

All BMs has a bandwidth of 8-bit and provide enable/disable control but there are three main factors that defines and differentiates between Bus Macros as provided by Xilinx

1. Signal Direction: As stated, communication between BDMs to PRMs is usually

through BMs and the logical data direction (input or output) is determined by the signal direction of a BM as well as its physical placement on the boarder of PRR. There are two main types of BMs in regard of signal direction *Left-to-Right* (L2R), which indicates that a signal flow in a BM is input from the left and output from the right side, and *Right-to-Left* (R2L) which indicates that a signal flow in a BM is input from the right in a BM is input from the right side and output from the left side. For Example to input data into a PRM using a L2R BM, it should be placed on the left side of the PRR. Virtex-4 devices can use two additional BM types, *Top-to-Bottom* (T2B) and *Bottom-to-Top* (B2T) which can be placed on the top or the bottom borders of the PRR depending on the logic direction of the signal passing through them.

- 2. Physical Width: The physical width of a BM indicates how much area does this BM uses when implemented and it has nothing to do with the bandwidth provided by this BM as all BMs provide a bandwidth of 8-bit regardless of thier type or physical width as indicated before. There are two types of BMs in regard of their physical width *Narrow*, which covers an area of two CLBs, and *Wide* which are four CLBs wide. The difference between narrow and wide BMs is that the wide BMs has two extra unoccupied CLBs as shown in fig (insert figure). These unoccupied CLBs inside a wide bus macro can be used for user logic or for additional wide bus macros, allowing wide bus macros to be staggered along a single CLB row. Wide bus macros nested in this fashion can provide up to 24 bits of bus macro bandwidth and need not be of the same type as L2R and R2L types can be mixed.

- 3. Synchronicity: In addition to the previously mentioned features that define a BM, whether signals passing through the BM are *synchronous* or *asynchronous* (i.e. registered or not registered) is another feature that also defines a BM. Synchronous BMs provide superiority over asynchronous ones in terms of timing performance and are recommended for designs that can afford some added latency.

Xilinx Provide BMs in the form of Pre-Place-and-Route hard macros with (.nmc) file

extension. The naming convention that Xilinx uses and recommends for BMs includes all the previously mentioned properties. For Example, the BM *busmacro\_xc2vp\_l2r\_async\_narrow.nmc* is Left-to-Right in direction, its physical width is Wide and asynchronous [30]. It can also be noticed from the name that it can be used with Virtex II Pro devices.

## Chapter 4: Implementation Methodology

### 4.1 Overview

Reconfigurable Platforms like FPGA chips provide hardware solutions that allow the end product to perform at high speeds that cannot be established through software solutions. But regardless of the amount of logic that you can have on an FPGA chip, it will always be limited resources and this is why efficiency in performance is usually measured by a combination of area and speed. This limitation in resources can be a problem when designing for hardware depending on the area consumed by a design and the amount of resources available on the target device on which the design will reside.

Partial Reconfiguration provides a solution for this problem as it can make use of the same area and resources to be used by different modules in the design without affecting other modules or their functionality. The idea is to find modules in the design that are not used all the time when the device is functional and implement them as reconfigurable modules so that they would be swapped with each other when requested. Not only that implementing the design in a reconfigurable fashion makes use of the available area efficiently, but it also produces more power efficient design implementations [5] as power consumption increases with the increase in area making this method suitable for light-weight implementations targeting low area devices which are powered by limited energy and power resources and should be very efficient in power and energy consumption.

We have built a system that makes use of partial reconfiguration and its benefits which is capable of performing IPSEC operations using reconfigurable modules. In addition to the previously mentioned advantages, implementing IPSEC using partial reconfiguration provides flexibility in the choices of algorithms or protocols available to an application as not all applications require all the operations that IPSEC offers. Within this system, we also implemented an embedded processor which is considered to be the static portion in the system along with its supporting peripherals to controls the reconfiguration procedure of the reconfigurable modules. The benefit of using an embedded processor can be summarized in the following point:

- It makes the system more autonomous as it is capable of self-reconfiguring the partial reconfigurable regions with modules requested by an application being processed.

- It allows faster response to changes happening in the system.

- It adds flexibility to the system by providing control over the system through software instructions using C language.

- Adding an embedded processor to the implementation could be free if the hard core embedded processor is used as it exists on the FPGA device anyway.

In the following sections, we will be discussing all modules in the system, their design descriptions and how they were integrated in the system.

## 4.2 Design Description Overview

As mentioned, the system is composed of static regions ,which include an embedded processor and some supporting peripherals, and reconfigurable regions, which include the reconfigurable modules of the IPSEC protocol. The design targeted two platforms, the Virtex-II Pro and the Virtex-4 devices described in the previous chapter along with their development boards. As both devices contain an embedded hard core PowerPC 405 processor, both the soft core (Microblaze) and hard core processors were used in different versions of the design.

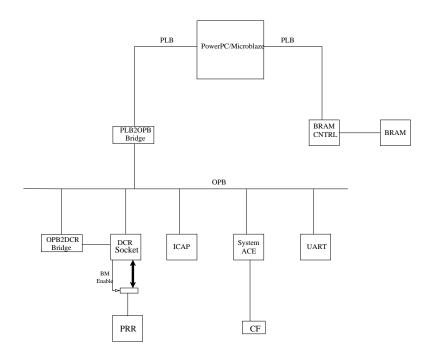

Figure 4.1: Embedded System Processor and Peripherals

The processor is connected to the BRAM-block peripheral through the Processor Local Bus (PLB) BRAM Interface Controller (BRAM\_IF\_Ctrl) which is interfaced as a Slave to the PLB Bus As shown in Figure 4.1. The BRAM-block peripheral gives the processor access to the BRAM components allowing data and instructions to be stored. The peripherals in the system are interfaced to the system through The On-chip Peripheral Bus (OPB) as Slave to the OPB. The peripherals in the system includes a Universal Asynchronous Receiver/Transmitter (UART), a System ACE and HWICAP. There is also a custom peripheral which represents the Partial Reconfigurable Region in the system that holds the Reconfigurable Modules. This custom peripheral is interfaced to the system through the Device Control Register (DCR) bus. There are also two bus bridges used, the plb2Opb\_bridge and opb2dcr\_bridge, to allow the communication between different buses in the system and the peripherals interfaced to them. This is a brief description of the system as it can be seen in Figure 4.1 and in the following sections we will be discussing the processors, buses and each peripheral in the system with more details.

## 4.3 Hardware Architecture

#### 4.3.1 Processor Cores and Buses

The basic components that define an embedded system are the microprocessor that controls the system and the buses on which data and instructions can be transfered from the microprocessor to other components and peripherals in the system. In this section we will describe the two processors which were used in different versions of our design and the buses associated with them.

#### **PowerPC** and Microblaze

In EDK, Xilinx offers two microprocessors to be used in embedded system designs PowerPC and Microblaze [31]. The PowerPC 405 (PPC405) is an embedded 32-bit hard core processor that was introduced by IBM to fit inside specialized applications like FPGA devices. The PPC405 can be found in the Virtex-II Pro and Virtex-4 FPGA devices. The main features of PPC405 can be summarized in the following points:

- A 32-bit Reduced Instruction Set Computer (RISC) processor core which has a 64bit architecture with 32-bit subset but only 32-bit implementations are included in embedded designing environments like EDK.

- It uses IBM User Instruction Set Architecture (UISA) for embedded environment.

- There are thirty two 32-bit General Purpose Registers (GPRs) for data and address operations.

- Five-stage pipeline with single-cycle execution of most instructions, including loads and stores.

- Two 16K 2-way set associative cache memories, instruction cache and data cache with eight words per cache line in each.

- Supports hardware debugging through forward and backward instruction tracing using Xilinx Microprocessor Debugger(XMD) and JTAG

- A Memory Management Unit (MMU) provides address translation, protection functions, and control for memory access.

Microblaze is an embedded 32-bit soft core processor introduced by Xilinx specifically for Xilinx FPGA devices. It can be implemented on any Xilinx FPGA device that can fit its size unlike PowerPC which can only be found in some of the Virtex devices. The main features of the Microblaze processor are:

- It is a 32-bit RISC-based processor core with few optimizations made by Xilinx for its FPGA implementations

- It has thirty two 32-bit GPRs to perform data and address operations

- Two different pipelining are supported, 3-stage and 5-stage single issue pipeline

- 32-bit instruction word with three operands and two addressing modes

- Optional direct mapped data and instruction cache memory

- Contains a MMU that was implemented based on PowerPC MMU architecture.

The advantages of using PPC405 is fast and has dedicated cache units and does not add overhead to the the design area consumption as it is already embedded in the FPGA but the disadvantage is that it is only implemented on few Xilinx devices where as Microblaze can be implemented in any FPGA device as long as it can fit its logic but the disadvantages is that it adds to the design area overhead.

#### **Core Bus Architecture**

The IBM CoreConnect bus architecture simplifies the integration and reuse of the processor system and peripheral cores within standard product and custom SoC designs [32]. This bus architecture includes three bus implementations

- Processor Local Bus (PLB): With 64-bit data width, the Xilinx PLB Version 3.4 consists of a bus control unit, a watchdog timer, and separate address, write, and read data path units with a a three-cycle only arbitration feature [33]. It is fully synchronous and supports 64/32-bit data transfer. It is mainly used to interface high speed peripherals and peripherals that are local to the processor like the instruction and data cache. Peripherals can be interfaced to the PLB bus through Master PLB (MPLB) interface or Slave PLB (SPLB) interface.

- On-chip Peripheral Bus (OPB): The OPB version 2.0 is a full-featured bus architecture with many features that increase bus performance [34]. It is fully synchronous and supports 32-bit data. It is used to interface different peripherals in the system with the processor and with each other by providing Master and Slave interface options to the bus (MOPB and SOPB). Although the OPB is not as fast as PLB, it can still be interfaced with it through a plb2opb\_bridge which allows the processor to communicate with the peripherals interfaced with the OPB.

- Device Control Register (DCR): The 32-bit wide DCR bus version 2.9 provides fully synchronous movement of GPR data between CPU and slave logic [35]. It provides the daisy-chain for the DCR data bus which allows the a single master to be directly connected to a number of slaves on the bus. The DCR has another important feature related to PR in which it interfaces the dcr\_socket to the OPB. The dcr\_socket disables bus macros during partial reconfiguration to prevent communication between the PRR and other Peripherals in the system until the new RM is completely configured. It can be interfaced with OPB bus through opb2dcr\_bridge to allow communication between peripherals in the system.

#### AES and SHA2 Cores

The PRR represents the peripheral in the system that is responsible for performing the functionality of the IPsec Protocol. As we discussed before, the protocol performs different functionality depending on the application being processed and the security service it demands. For example, if the application requires confidentiality then the data in the application should be encrypted to assure confidentiality and if the application requires integrity then a hash value is calculated from the application data using a hash function and send it with the original data. For these security services to be provided, the IPsec uses a number of cryptographic algorithms like the Advanced Encryption Standard (AES) with 128-bit key which assures confidentiality is provided by the system and Hash-Message Authentication Code with Secure Hash Algorithm 256 (HMAC-SHA-256) to assure data integrity and authentication are provided by the system. The AES is a symmetric key cipher which uses the same key for encryption and decryption. There are four main operations that take place during encryption of a data and the inverse of these operations is used during decryption. These four operations as described in [36] are as follows:

- 1. SubBytes: The subBytes transformation is a non-linear byte substitution that operates independently on each byte of the State using a substitution table (S-box).

- 2. ShiftRows: In this transformation, the bytes in the last three rows of the State are cyclically shifted over different numbers of bytes (offsets).

- 3. MixColumns: The MixColumns transformation is a mixing operation which operates on the columns of the state, combining the four bytes in each column.

- 4. AddRoundKey: In the AddRoundKey transformation, a Round Key is added to the State by a simple bitwise XOR operation.

We implemented the AES core in hardware as a RM in the PRR region that represents the hardware accelerator for the IPsec protocol in the system. The datapath for AES encryption module is 128-bits as shown in Figure 4.2. The state register is also used for debugging purposes during the hardware/software synchronization to determine the current state of AES. Figure 4.3 shows the top-level view for the datapath/controller signal communication along with the interface with the design top-level.

Figure 4.2: AES DataPath.

On top of the AES datapath, we created a wrapper to give the datapath an 8-bit interface through Single Input/ Parallel Output (SIPO) for the input data and Parallel input/ Single output (PISO) for the output as shown in Figure 4.4. It is also used to interpret whether the input is actual data or key depending on the command send before the data to wr\_cmd. The input is interpreted as key if the value 0x40 was sent before the input and it is interpreted as data if it was preceded by the value 0x80.

Figure 4.3: Top-Level Diagram for AES Encryption Module.

Figure 4.4: Top-Level Diagram for AES Wrapper

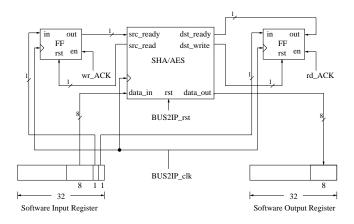

The AES wrapper is interfaced to the embedded system through the OPB bus in the user\_logic as shown in Figure 4.5 as well as the controller/datapath top-level view.

Figure 4.5: AES Wrapper

The HMAC is a combination of Message Authentication Code (MAC) and a hash function to ensure data integrity and authenticity of a message, it is also known as keyed hash functions [37] as they perform all hash function operations but they also use a key to assure authentication. The HMAC operates in the following way:

- 1. The key is added to a known value specified in [37] HMAC standard known as I-PAD using simple bitwise XOR operation.

- 2. The output I-KEY-PAD from the previous step is padded with the message and input to the hash function

- 3. The key is also added to another constant value specified in [37] known as O-PAD in the same way as step one

- 4. The output O-KEY-PAD from step 3 is padded with the hash value calculated in step 2 and the padded value is input again to the hash function

#### 5. The output from the hash function is the calculated HMAC value.

Figure 4.6: SHA-256 Datapath

Due to the fact that any hash functions can be used to calculate HMAC value, The hash function that is being used to calculate a HMAC value should be added to the HMAC name i.e. HMAC-MD5 indicates that MD5 hash function is being used to perform HMAC calculations. As IPsec protocol supports different hash functions to be used for HMAC calculation, Secure Hash Algorithm 256 (SHA-256) is the hash function we used for HMAC calculations. Figure 4.6 illustrates the SHA-256 datapath we implemented to be used as another RM in the PRR region to perform the hash function operations to calculate HMAC as a service provided by the IPsec protocol. The datapath is 256-bit with a 32-bit interface to the datapath wrapper through PISO similar to AES. The datapath wrapper shown in Figure 4.7 uses SIPO and PISO to interface the 32-bit output from the datapath to the common interface it shares with AES. The top-level for the SHA-256 Wrapper shown in

Figure 4.8(controller/datapath) has the exact same interface as the AES as so that they can share the same PRR.

Figure 4.7: SHA-256 Datapath

Figure 4.8: SHA-256 Wrapper

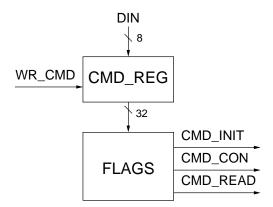

Since hash functions do not use keys for hash calculations, the wr\_cmd shown in Figure 4.9 is used by SHA-256 controller to determine whether the incoming block is for new data or it is the next block for the previous data.

Figure 4.9: SHA-256 Command Flag

#### Hardware Internal Configuration Access Port

As discussed before, the ICAP gives the user design the ability to write the configuration memory during run-time which makes it a useful configuration technique for partial reconfiguration. The Hardware Internal Configuration Access Port (HWICAP) is the hardware peripheral that enables the embedded processor in the system (PowerPC or Microblaze) to access and modify the configuration memory while the circuit is operational through the ICAP. The HWICAP is also known as OPB-HWICAP as it is interfaced with the embedded processor and other peripherals in the system through the OPB bus interface as shown in Figure 3.3. At run time when the system needs to swap an existing RM with another, HW-ICAP fetches the partial bitstream from the external memory frame by frame and sends it to the desired CLBs in the PRR to perform partial reconfiguration of the system. For the HWICAP to perform correctly, the ICAP interface should be enabled through configuration mode pin setting and software.

#### **Other Peripherals**

In addition to the peripherals mentioned, there are other auxiliary peripherals interfaced to the system through the OPB Slave interface (SOPB) as follows:

- Universal Asynchronous Receiver/Transmitter: The Recommended Standard 232 (RS232) is interfaced with the system through opb\_uartlite peripheral. Using a serial cable and a PC, the opb\_uartlite can transfer characters to a standard VT100 terminal (like HyperTerminal) or communicate with other external devices that has the RS232 interface. Different baudrates are supported by the opb\_uartlite peripheral in EDK but the same baudrate should be set for the terminal program as well for data transmission to be successful.

- System ACE: As mentioned, partial bitstreams that are being used to reconfigure the PRR with PMs needs to be stored in an external memory. A FAT32 Compact Flash (CF) memory card is used as the non-volatile memory that holds the partial bitstreams and it is being interfaced with the system through opb\_sysace to allow the loading and swapping between different PMs.

- DCR Socket: The opb\_dcr\_socket peripheral plays an important role in a partial reconfigurable design. It disables the bus macros during partial reconfiguration of the PRR through ICAP to prevent signal from passing from the static region to the PRR and the other way around. Without the existence of such mechanism, a successful partial reconfiguration would not occur.

#### 4.3.2 Software Architecture

#### Overview

As much as the hardware portion is to an embedded system, the software portion is of equal importance to the system. In addition to the software drivers for the hardware peripherals in the system and some basic C libraries, EDK has a GNU Compiler Collection (GCC) which supports C/C++ software programming languages to compile user written C codes into opcode instructions for the embedded system processor (PowerPC or Microblaze). The software that we wrote performs a number of tasks including

- Initialization of the system, ICAP and HWICAP

- An API for the RS232 Serial interface to read data from user and send output to HyperTerminal

- ICAP API to fetch partial bitstreams from CF card and reconfigures the PRR

- Sending and receiving data to and from AES and SHA-256 cores

- Preparing data before being sent to SAH256 core for HMAC calculations

In this section we will illustrate some of the tasks mentioned above in more details showing the software/hardware communication and how partial reconfiguration is managed through software.

#### HMAC-SHA-256 Padding

As HMAC can be calculated for any message, there should be certain steps, as mentioned in the previous section, that should be followed for a message to prepare it for the calculation. calculation of HMAC can be represented by the following formula

$$HMAC(k,m) = h((k \oplus opad) / / h((k \oplus ipad) / / m))$$

where m is the input message to calculate the HMAC value for, h is the hash function, k is the secret key and *opad* and *ipad* are the outer and inner padding constants respectively.